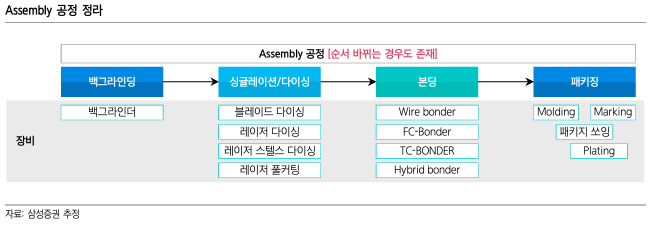

지난 포스팅의 백그라인디과 다이싱에 이어서 본딩, 패키징, 외관.

본딩과 패키징은 엄밀히 따로 분리하지는 않는 것으로 보인다.

기본적으로 본딩은 반도체 소자(칩)와 기판을 연결하는 것으로

실제 반도체에 신호를 주고받는 다리 역할을 한다.

다리만 연결한 체로 반도체를 사용하는 것이 아니고 포장(패키징)까지 해야 실질적인 사용 가능한 상태이기 때문.

따라서, 본딩과 패키징은 별도로 구분하지 않고 하나로 묶으며,

반도체 제품 외관에 대한 공정도 다룬다.

※ 삼성증권

※ 삼성증권

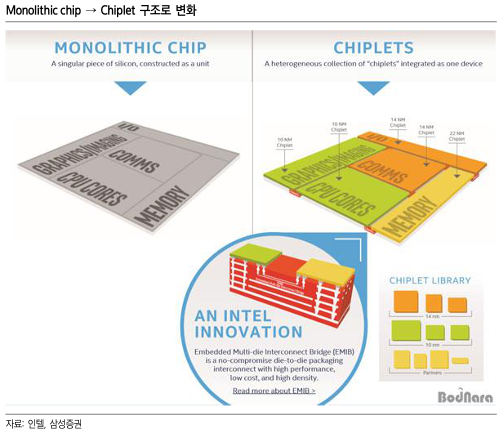

반도체의 본딩과 패키징은 chiplet 구조의 등장으로 중요도가 상승했다.

반도체의 미세화와 고도화로 생산 난이도가 증가하면서

단일 소자(Monolithic chip)로 원하는 성능을 내는 반도체를 만들기가 어려워졌다.

따라서 여러 종류의 반도체 따로(IP block) 만든 후

서로 다른 반도체들을 함께 포장(패키징)을 해서 하나의 반도체(chiplet)을 만들게 되었다.

이런 패키징 과정에서 다양한 방법이 고안되었다.

패키징 기술의 Wire Bonding Packaging → Flip Chip Packaing → Wafer Level Packaging → Panel Level Packaging → Heterogeneous Packaging으로 발전했다.

반도체의 외관 공정도 패키징으로 구분한다

외관 공정은 반도체를 포장하는 Encapsulation 공정과 마킹 공정으로 나눈다.

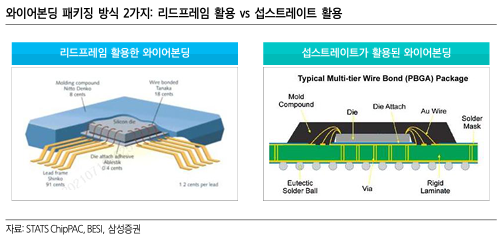

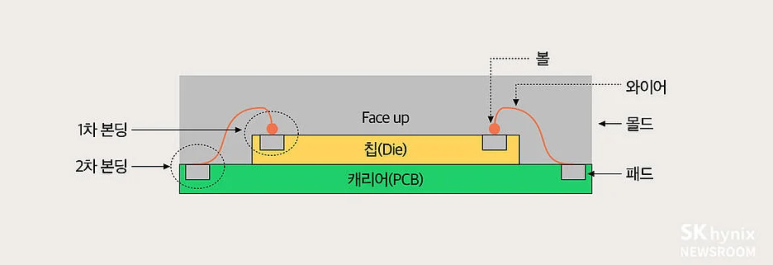

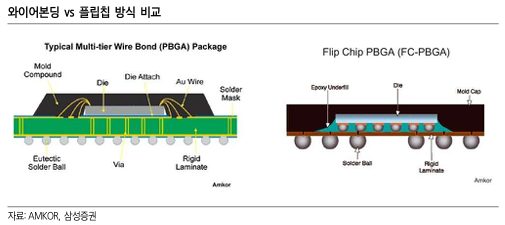

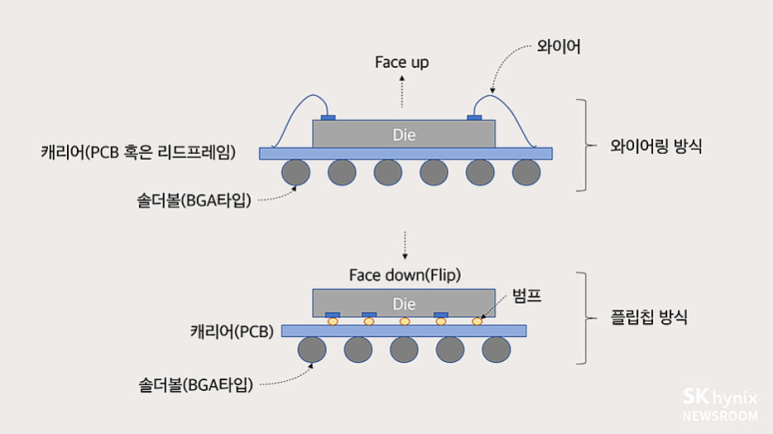

1. Wire Bonding Packaging

※ 삼성증권

※ SK하이닉스 뉴스룸

- 리드프레임이라는 전선 형태로 본딩

- I/O가 제한적

- 가장 난이도가 쉬운 기술로 진입 장벽도 낮음

- 70 % ~80 %의 점유율을 가지고 있지만 ASP도 낮음

2. Flip Chip Packaging (FC Packaging)

※ 삼성증권

※ SK하이닉스 뉴스룸

- 반도체를 뒤집어서 (flip chip) 하여 기판과 연결하는 방법

- 반도체 아래에 redistibution layer(RDL)를 추가

- Wafer bump를 이용해 기판과 연결

- Wire bonding에 비해 I/O가 증가, 속도 증가

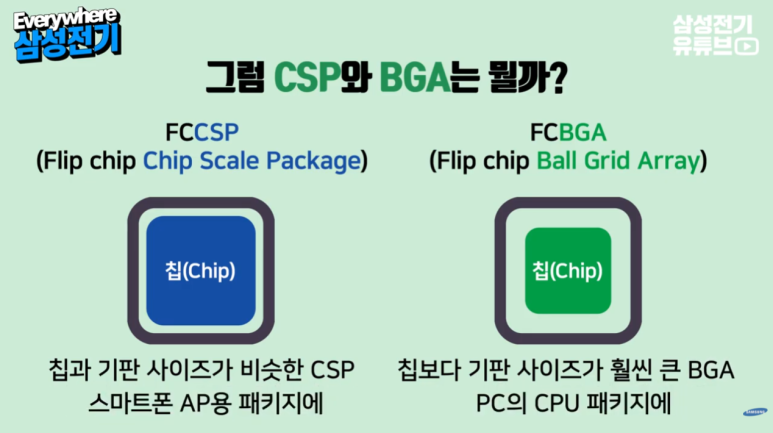

※ 삼성전기 유튜브

- Flip Chip Bonding을 이용하는 패키징은 크게 두 가지

* Flip Chip Chip Scale Package (FC-CSP): 반도체와 기판 사이즈가 비슷. 작고 얇은 폼팩터가 필요한 경우.

* Flip Chip Ball Grid Array (FC-BGA): 반도체보다 기판이 큰 경우. 고성능, 많은 I/O가 필요한 경우.

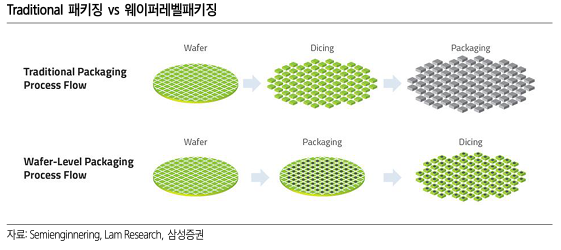

3. Wafer Level Packaging (WLP)

※ 삼성증권

- 웨이퍼에서 다이싱 후 개별 칩을 패키징 하는 전통적인 방법이 아닌,

- 웨이퍼 단에서 페이징 후 다이싱하여 개별 칩을 만드는 방법

- RDL package, flip chip package, TSV package 등을 웨이퍼 단에서 하면 모두 WLP에 속함 (TSV는 후술함)

- 비용 절감, 작은 사이즈 칩에 대응 가능

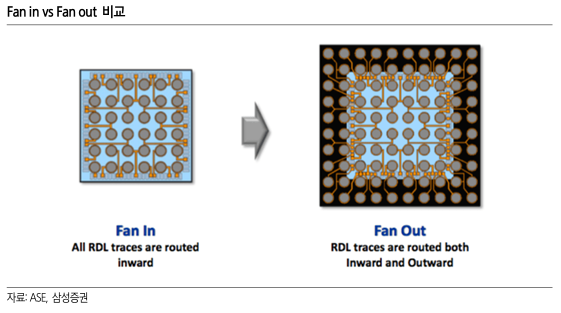

※ 삼성증권

- WLP는 크게 두 가지로 나뉨

* Fan-In Wafer Level Package (FI-WLP)

· 칩 크기와 패키지 크기가 거의 유사하여 칩 안에 I/O가 배치

· I/O 수가 제한적이지만, 비용 절감 가능

*Fan-Out Wafer Level Package (FO-WLP)

· 칩 크기보다 패키지 크기가 거서 칩 바깥쪽에 패키지 I/O가 배치

· 많은 I/O 확보 가능

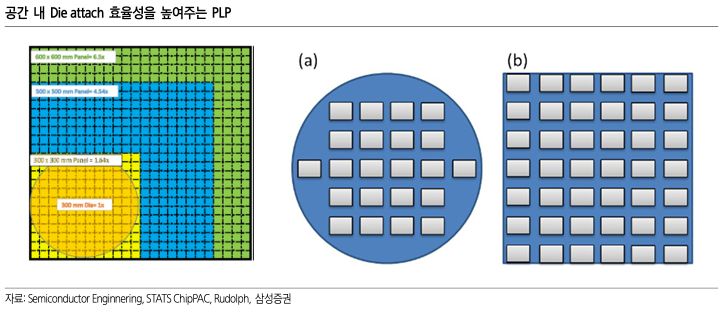

4. (Fan-Out) Panel Level Packaging (FO-PLP, PLP)

※ 삼성증권

- Fan-Out 방식을 극대화하기 위해 고안된 방법

- 원형인 웨이퍼 위에서 패키징을 하는 것이 아닌 정사각형의 panel 위에서 패키징

- 패키징 효율을 높이기 위한 방법 (원형의 웨이퍼 대비 버려지는 영역이 적음)

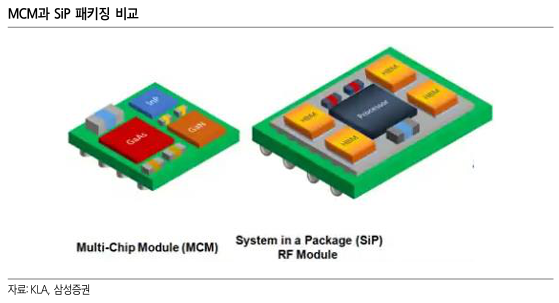

5. Heterogeneous Packaging (이종 패키징)

- (2D) Multi - Chip - Module

※ 삼성증권

* 기판 위 평면(2D)에 반도체를 배치하는 방식

* 기존 MCM 방식

· 각각의 패키징 된 칩들을 본딩이나 범핑으로 연결: 선 패키징, 후 연결

* System in a Package (SiP) 방식

· 본딩이나 범핑으로 칩들을 연결 후 패키징: 선 연결, 후 패키징

· 수동소자를 함께 패키징 가능하며, 폼팩터의 소형화 가능

· 인터포저와 TSV에서 활용 가능한 방법 (후술함)

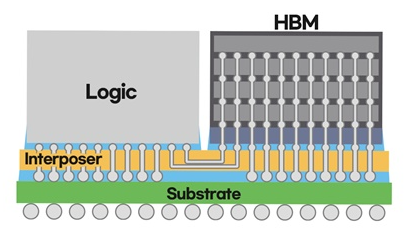

- (2.5D) Si Interposer

※ 삼성전자 뉴스룸

* 칩과 기판의 회로 폭 차이를 완충시키는 역할

* 칩과 기판을 연결하는 추가적인 미세 회로 (그림의 노란색 영역)

· 칩의 I/O:기판 I/O = 20:1

* 상호 연결 속도와 대역폭은 높이면서, 지연성과 전력 소모는 감소

* 대용품으로 Si Bridge, organic interposer가 개발 중이지만 비용과 수율의 문제가 있음

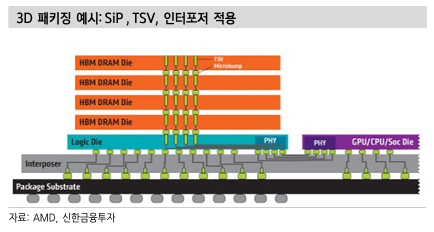

- (3D) Through Silicon Via (TSV)

※ 신한금융투자

* 반도체를 적층 구조로 쌓은 후, 실리콘을 관통시켜 연결하는 방식 (HBM DRAM Die를 연결하는 영역)

* 칩 내부에서 도통 되기 때문에 I/O 제한이 적으며 응답 속도가 빠름

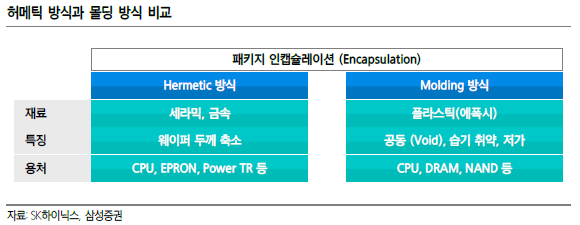

6. Encapsulation 공정

반도체 패키지를 봉합하는 공정으로 반도체를 외부환경으로 보호하기 위함다.

크게 Hermetic 방식과 Molding 방식이 있다.

※ 삼성증권

현재는 대부분 몰딩 방식을 이용한다.

Molding 방식은 EMC (Epoxy Molding Compound)라는 소재를 이용하며,

반도체 동작 시 발생하는 열을 방출시키면서 반도체와 유사하게 팽창하는 것이 중요하다.

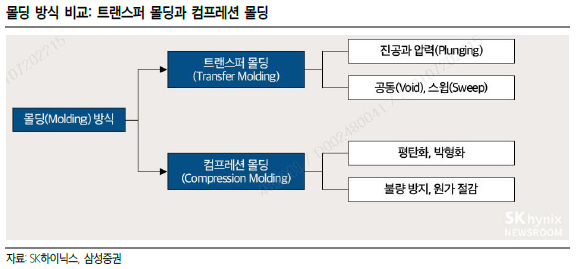

몰딩 방식에는 전통적인 트랜스퍼 몰딩이 있고 컴프레션 몰딩이 있다.

※ 삼성증권

7. Marking 공정

마킹 공정은 반도체 외관에 반도체의 제품명, 시리얼 번호, 작동 정보, 제조사 등의 정보를 표시하는 공정이다.

레이저를 이용해 음각을 하는 방법과,

잉크를 이용해 양각을 하는 방법이 있다.

최근 반도체가 monolith 구조에서 chiplet 구조가 되면서 시장도 점차 커지고 있다.

하나의SoC 위에 여러 반도체가 올라기 때문에 각 반도체의 IP Block에 정보 표기가 필요하다.

※ 삼성전자 뉴스룸

※ 삼성전기 유튜브

※ SK하이닉스 뉴스룸

※이베스트투자증권 최영산 - Over the Horizon II (2020. 9. 14)

※한국과학기술기획평가원 - 반도체 후공정(패키징) (2020-16호)

※Teradyne - Financial Results for Q2 2021

※삼성증권 배현기 - 반도체 후공정: 달라지는 위상, 새로워질 평가 (2021. 8. 11)

※신한금융투자 기업분석부 - 2021 OSAT Wave (2021. 1. 22)

OSAT를 공부하자 - Intro

OSAT를 공부하자 - Assembly & Packaging: 백그라인딩 & 다이싱

OSAT를 공부하자 - Test

Disclaimer

- 당사의 모든 콘텐츠는 저작권법의 보호를 받은바, 무단 전재, 복사, 배포 등을 금합니다.

- 콘텐츠에 수록된 내용은 개인적인 견해로서, 당사 및 크리에이터는 그 정확성이나 완전성을 보장할 수 없습니다. 따라서 어떠한 경우에도 본 콘텐츠는 고객의 투자 결과에 대한 법적 책임소재에 대한 증빙 자료로 사용될 수 없습니다.

- 모든 콘텐츠는 외부의 부당한 압력이나 간섭없이 크리에이터의 의견이 반영되었음을 밝힙니다.