해기사투자자의 팜

[반도체산업] 1편. 기초부터 트렌드까지

해기사투자자

2023.05.20

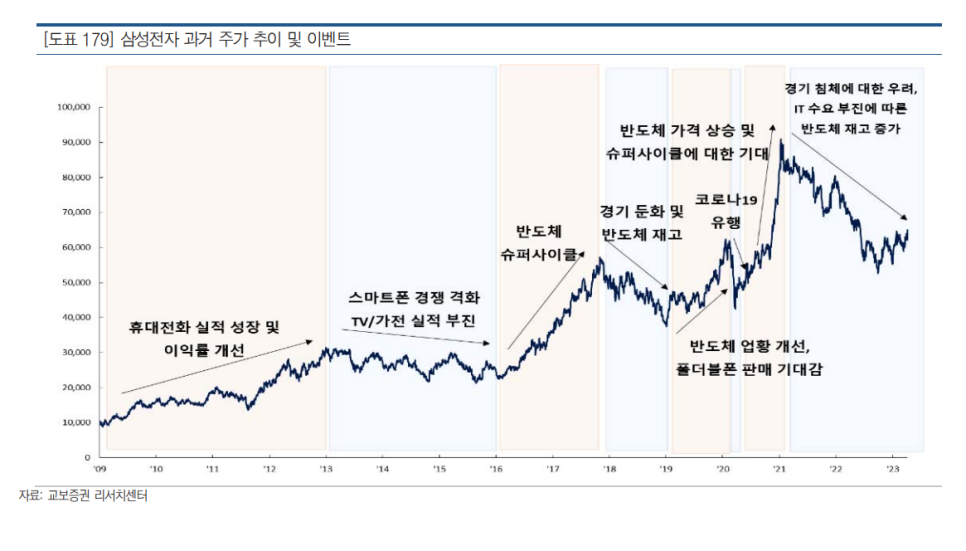

주식 투자를 시작하고 처음으로 공부했던 산업. 기술에 대한 지식이 많이 늘면서 지적 유희를 느끼게 된 공부였는데, 범위가 넓어 시간이 좀만 지나도 새롭게 보일 때가 많다. 작년부터 메모리 사이클과 디커플링된 기업들이 많아지면서 메모리 사이클과 상관없이 엣지있는 기업들이 나오고 있어 사이클이 무슨 상관이겠냐 할 수도 있지만, 메모리 사이클이 달리면 100% 수익률은 기본으로 가져가는 기업들이 많아질거라고 본다. 개인적으로는 올해가 중요하다고 보고, 지금 산업정리를 제대로 하고자 한다.

(반도체 섹터는 워낙 광범위하기 때문에, 베이스에 초점을 두고 기술에 대해서는 간단히만 하여 글을 썼습니다. 그리고 반도체 산업은 국내 주식시장에서 큰 비중을 차지하기 때문에 고수분들 및 증권사 연구원님들이 좋은 자료를 많이 배포해주셨습니다. 자세한 내용을 알고 싶으시다면 각 항목에 맞는 좋은 글들을 첨부했으니 참고하시길 바랍니다)

<목차>

#1편

0. 반도체 용어

1. 반도체 기초

1.1 반도체란(BASIC)

1.2 메모리

1.3 비메모리

1.4 반도체 기업 세분화

1.5 반도체 기술 및 원리(HARD)

1.6 반도체 갖가지

2. 반도체 공정

2.1 전공정

2.2 후공정

2.3 기타공정

3. 기판 및 PCB

4. 반도체 사이클 및 주가

4.1 반도체 사이클

4.2 엣지에 대한 프리미엄

5. 반도체 트렌드/변화

5.1 반도체 자국화

5.2 미세화

5.3 어드밴스드 패키징

5.4 화합물 반도체

5.5 HBM

5.6 3D DRAM

----------------

#2편

6. 반도체 제조 기업

7. 반도체 소재 기업

8. 반도체 부품 기업

9. 반도체 장비 기업

10. 반도체 기타 기업

11. 반도체 기판(PCB) 기업

12. 반도체 OSAT 기업

13. 반도체 전방 기업(고객사들)

14. 반도체 대가들

<글을 안내하며...>

간단한 산업 분석으로 시작한 글에 욕심이 붙어 서순과 정갈함에 아쉬움이 큰 글이 되었고, 시간이 많이 걸려 2편에 걸쳐 작성하게 되었습니다. 많은 지식이 주식 성공을 보장하지는 않으나, 한번 공부하는겸 '이해'에 초점을 맞추고 동시에 많은 내용을 담고자 노력했습니다. 인생 처음 들어보는 기술적 용어나 머릿속에 떠오르기 어려운 소부장이 많고, 카테고리 분류가 애매해서 반복되는 내용이 많습니다. 외우기보다는 친숙화에 중점을 두고 읽으심을 추천드립니다. 본 포스팅을 2개의 창으로 띄어서 하나는 쭉 읽어나가는 용, 다른 하나는 용어나 헷갈리는 부분을 다시 짚는용으로 하시면 더욱 더 맛있게 즐기실 수 있습니다.

반도체 산업은 글로벌로 멈추지 않고 연구개발이 이뤄지고 있습니다. 그렇기에 발전이 지속되는 대표적인 산업으로, 크게 2가지의 길에서 변화가 일어나고 있습니다. 하나는 소재, 다른 하나는 공정입니다. 각각의 흐름을 나눠 정리하시면 전체적인 반도체 로드맵이 그려지실 겁니다(설계도 변화가 일어나고 있지만, 투자자 입장에서 접근하기는 쉽지 않다고 생각하네요).

(본 포스팅에서 로 칠해져 있는 부분은 중요한 부분이고, 로 칠해져 있는 부분은 기업의 제품과 직접적으로 연관된 부분입니다.)

0. 반도체 용어

0.1 아주 기초적인

실리콘: 반도체에서 말하는 실리콘은 원소기호 Si(규소)를 의미함. 우리 일상에서 보는 접착제나 보형물 그거랑 다른거임.

가속기(ACCELERATOR): 메인 프로세서를 보조하는 장치 및 반도체.

IP: 지적 재산권

HDD: 하드 디스크 드라이브. 비휘발성 데이터 저장소로 대중적이고 가격이 저렴하다. 자기장의 원리로 동작하기 때문에 반도체가 아니다.

PCB: 인쇄회로기판. 전자기기의 부품간에 전기적인 연결을 하는 기판이다.

마더보드: 국내에선 메인보드로 통용되며, 전자기기의 PCB들 중에서 메인이되는 보드를 의미한다.

마이크로프로세서:

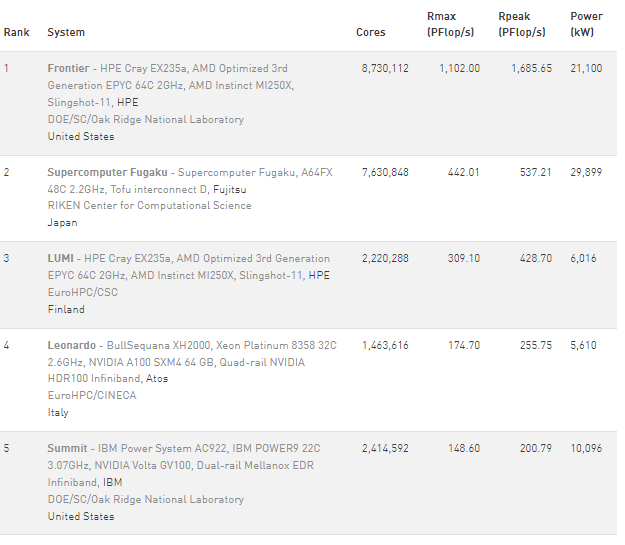

HPC: 슈퍼컴퓨터. 대규모의 연산을 초고속으로 수행하는 컴퓨터.

I/O: INPUT/OUTPUT

IC: 집적회로. 반도체 기판 또는 칩, 회로를 일컫는 용어다. 사실상 우리가 반도체라고 부르는 제품들은 IC이다. 반도체 섹터를 볼 때는 'IC=반도체=칩' 이라고 보면 된다.

트랜지스터: 반도체 소자. 일상에서는 반도체=트랜지스터라고 하는데, 반도체 공정에서 트랜지스터는 반도체를 이루는 집적회로 중 하나의 소자를 말한다. 현재는 트랜지스터 수억개가 집적되어 반도체를 이룬다고 보면 된다.

임베디드시스템: 범용목적의 PC와 다르게, 특정한 제어를 위해 수행하는 컴퓨터 시스템(집적회로). 키오스크, 가전제품에 들어가는 시스템이 그러하다.

대역폭: 데이터의 최대 전송 속도. 전자/진동공학에서는 다른 의미로 씀.

코어: 반도체가 실제 일을 하는 단위.

클럭: 반도체가 1초당 처리하는 데이터의 양을 Hz로 나타낸 것.

유닛그로쓰: 물량의 증가를 나타냄.

비트그로쓰: 물량들을 비트 단위로 환산해서 용량의 증가를 나타냄. 반도체는 스펙이 계속해서 증가하므로 비트그로쓰를 체킹하는게 중요.

전구체: 어떤 물질을 만드는데 필요한 주요 소재.

에천트: 식각액. 식각에 필요한 화학물질들을 통칭하기도 한다.

0.2 알면 좋지만 어려워

전하: 자유전자의 이동으로 전기적인 성질을 띠게 된 전자와 양성자. 양성자가 많으면 양전하, 전자가 많으면 음전하. 그래서 전하는 양수나 음수로 표현 가능함. 질량같이 물리적인 특성을 표현한 용어인데, 전기적 성질을 물리량으로 표현한 것이라고 보면 됨.

유전체(dielectric): 부도체가 완전히 전기가 통하지 않는 말이 아님. 부도체는 저항이 높아서 전기가 통하지 않는 것인데, 그것을 뚫을 정도의 전압을 걸면 전류가 흐르게 됨. 즉, 유전체는 외부로부터 전기장이 가해지면 분극이 되는 물질임. 분극은 물질 내에 (+)와 (-)전하가 나뉘는 것임. 절연체이어야 유전체가 될 수 있다.

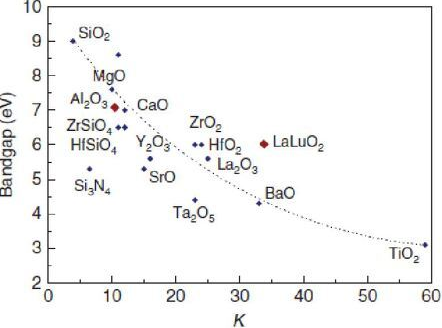

유전율(K): 유전체가 얼마나 분극이 잘 일어나는지를 나타내는 지표. 높을수록 분극을 잘한다 > 외부의 전기장을 잘 감소시킨다. 유전율이 높으면 정전용량이 높아진다 > 더 많은 전하를 저장할 수 있다.

High-k: 유전율이 높은 물질.

LOW-k: 유전율이 낮은 물질. 전기가 빠르게 이동하는 배선과 배선 사이를 채우는 곳에 절연막으로 많이 쓰인다.

정전용량(캐패시턴스): 캐피시터의 전하를 축적할 수 있는 능력.

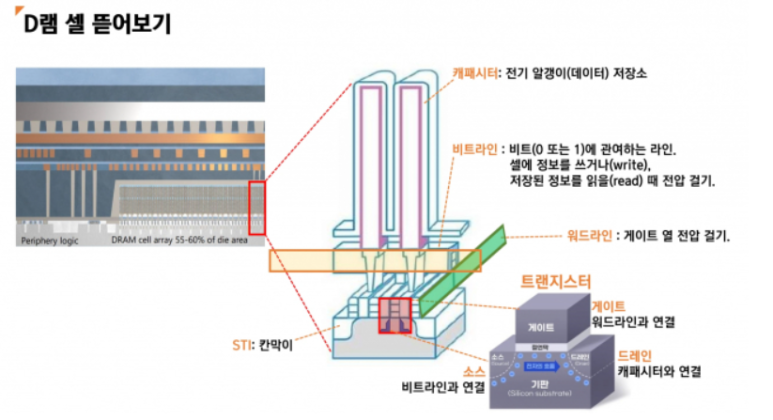

커패시터(콘덴서): 전하를 저장하는 곳. 2차전지와 달리, 전하 그 자체를 저장하기 때문에 충/방전속도에 한계가 없다. 금속판 사이에 유전체가 채워져 있는 형태임. 유전체에 따라 분극(충/방전)의 빠르기나 충전할 수 있는 전하량이 달라지는 것임=유전율이 높으면 충방전 정도가 높아진다. D램의 캐패시터는 전하를 잘 들고 있기 위해 High-K를 쓴다.

절연: 전류를 차단하는 것.

비트라인:읽기나 쓰기 동작시에 셀 외부와 내부 사이에 데이터가 이동하는 통로이다. 신호 (0,1)을 전달한다.

워드라인: 게이트의 ON/OFF를 조절하는 통로다.

D램의 트렌치형: 실리콘 기판에 홈을 파서 캐패시터를 기판 내부에 형성.

D램의 스택형: 실리콘 기판 위에 3차원 구조의 캐패시터를 쌓아 올리는 구조. 이걸로 삼전이 D램시장을 선두하였다.

PIM: Processing in Memory, 메모리 반도체에 연산기능을 탑재. PNM=Processing near Memory. CMS=Computatonal Memory Solution. 다 비슷한 용어다.

0.3 공정 디테일

잉곳: 모래에서 규소를 추출하고 고온의 열로 용해하여 실리콘 용액을 추출한 후 만든 덩어리.

다결정잉곳: 효율성이 떨어져 태양광 산업에 주로 씀.

단결정잉곳: 반도체에 주로 쓰는 잉곳.

웨이퍼: 잉곳을 얇게 절단한 실리콘 기판.

싱글타입: 웨이퍼를 하나씩 투입하여 진행하는 경우.

배치타입: 웨이퍼를 다발로 투입하여 진행하는 경우.

반사경: 광학계에서는 거울도 반사렌즈라고 한다.

SiO2: 실리콘 산화막(이산화규소). Si보다 높은 유전율과 밴드 갭으로 효과적인 절연체 역할을 한다.

STI: 트랜지스터 간에 서로 간섭을 하지 못하게 하는 칸막이. 주로 SiO2로 만들어진다.

Si3N4: 실리콘 질화막.

옥사이드: 산화물. 산소와 다른 원소의 화합물. 반도체에서 절연체 용도로 쓰인다.

폴리실리콘: 다결정 실리콘.

PR: Photoresist. 감광액.

디펙(Defect): 결함.

TAT: 웨이퍼 투입부터 최종 공정 완료까지 걸리는 공정시간. 최소 3개월에서 길게는 6개월이 걸린다.

폴리실리콘: 다결정 실리콘. 반도체웨이퍼는 단결정을 채택하지만, 반도체의 전도체나 전극으로는 많이 쓰인다.

비아(via): 구멍을 의미. 배선이 통하는 통로인데, 반도체 칩의 금속배선이나 다층 PCB의 연결통로를 말한다.

종횡비: Aspect ratio. 물체 가로와 세로의 비.

등방성: 모든 방향에서 식각 속도가 같은 것. 원하지 않는 곳도 깎인다.

비등방성(=이방성): 수직과 수평간 식각속도가 다른 것. 원하는 곳만 깎을 수 있다.

CCP: Capacitively Coupled Plasma. 단단한 물질 식각에 유리.

ICP: Inductuvely Coupled Plasma. 균일한 식각에 유리.

IMD: Inter-Metal dielectric. 금속 배선의 합선을 방지하기 위한 절연층.

ILD: Inter layer dielectric. DRAM 캐피서터 층간 절연층.

Passivation: 반도체 칩에 유해한 환경을 차단하는 것.

Trench와 stack: 트렌치는 실리콘 웨이퍼에 홈을 파서 기판 내부에 형성하는 방식. 스택은 실리콘 웨이퍼 위에 3차원 구조로 쌓는 방식.

0.4 기업 관련

삼전: 삼성전자

삼성 시스템LSI사업부: 삼성전자 내 비메모리 사업을 영위하는 곳.

세메스: 삼성전자 자회사. 반도체 및 디스플레이 장비 생산업체. 국내 1다.

SKH: SK하이닉스

ON-SEMI: 온세미컨덕터(일본)

TI: 텍사스 인스트루먼트(미국)

STM: STMicro(스위스)

LAM: 램리서치(미국)

TEL: 도쿄 일렉트론(일본)

AMAT: (미국)

Coherent: 구 II-VI(미국)

SiCrystal: Rohm 자회사(일본)

리조넥: 옛 쇼와덴코

1. 반도체 기초

1.1 반도체란(기초)

반도체의 사전적 정의는 말 그대로 반만 도체인 물체이다. 도체는 전기가 통하는 물질, 부도체는 전기가 안 통하는 물질인데 특정 조건에서는 도체가 되고 아닌 경우에는 부도체가 되는 물체라고 볼 수 있다. 스위치와 같은 역할을 한다고 볼 수 있다.

하지만 우리가 칩이라고 알고 있는 반도체는 사전적 정의보다 더 좁은 개념으로, '반도체의 특성을 가진 회로가 박힌 전자칩' 이라고 보면 될 듯 하다. 이 반도체 칩은 반도체의 성질을 가진 원소인 Si(규소), Ge(저마늄)에 P(인)나 B(붕소)와 같은 불순물을 넣어 만들어진다.

최근에는 13족 및 15족 원소가 결합된 화합물 반도체도 많이 만들어지고 있다(5.4항목 참고).

1) 반도체 다이

반도체 '다이'는 반도체 '칩'과 혼용되어 사용되는데, 개념은 비슷하나 다른 용어다. 다이는 전공정에서 SAWING(자르기) 전에, 웨이퍼에서 각각의 집적 회로를 말하는 것이고, 칩은 후공정에서 SAWING 되고 개별적으로 구분된 상태를 의미한다.

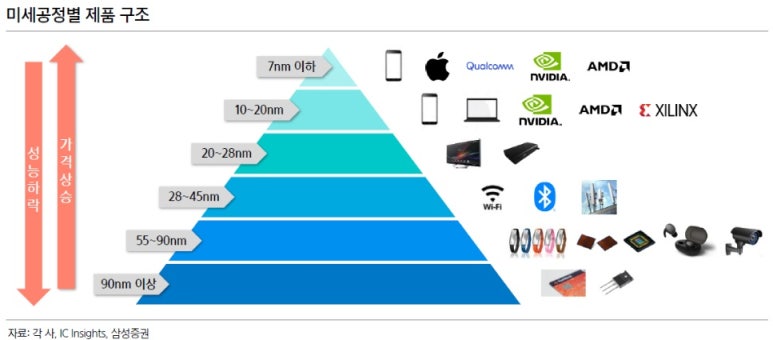

여기서 넷다이라는 용어로 이어지는데, 넷다이는 웨이퍼상에서 나올 수 있는 다이의 수를 말한다. 넷다이가 중요한 이유는, 다이 사이즈가 작을수록 넷다이는 커지고 고정비 레버리지가 나올 수 있기 때문이다. 그렇기 때문에 미세화가 더욱 중요해지는 것이고, 팹리스 입장에서는 미세화 기술이 뛰어난 파운드리에 맡길수록 웨이퍼당 많은 다이를 뽑아낼 수 있다.

또한 넷다이가 많을수록, 수율도 높다.

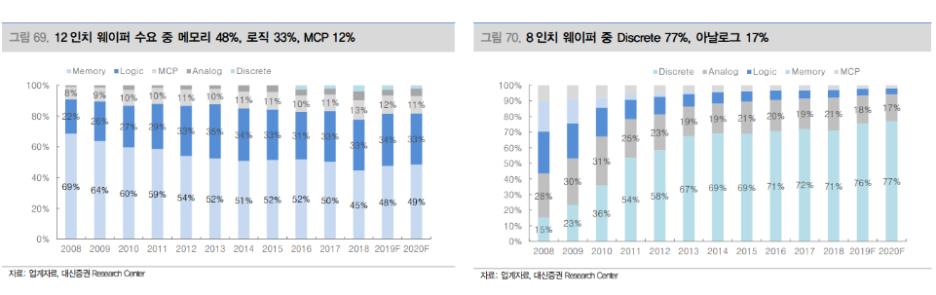

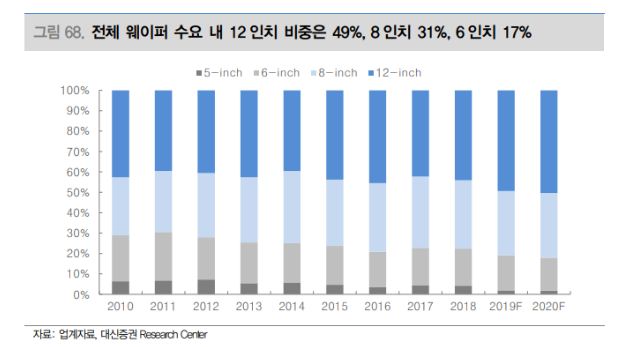

2) 웨이퍼 크기

웨이퍼는 크면 클수록 생산율이 높아져 여러가지 장점이 있지만, 웨이퍼 크기에 따라 설비 자체가 많이 바뀌기 때문에 만들어지는 칩에 따라 크기를 달리한다. 대표적인 웨이퍼 크기는 6인치(지름150mm) > 8인치(200mm) > 12인치(300mm)가 있다.

12인치는 소품종 다량생산에, 6/8인치는 다품종 소량생산에 특화되어 있다고 하는데, 이는 다품종 제품들이 대부분 간단한 소자나 칩인 경우가 많기 때문이다. 그리고 반도체 선단노드는 웨이퍼에 많은 비용이 들어가기 때문에, 생산율이 높은 12인치를 주로 채택한다.

6/8인치는 레거시 칩을 생산하고, 시장이 오래되었다보니 서열정리가 되었다. 그래서 후방격인 소부장들은 재미가 없으니 6/8인치 팹을 무시하게 되고, 6/8인치 웨이퍼에서 나온 칩들의 수요가 터지면 공급이 따라가질 못해 쇼티지 현상이 발생하는 것이다(2020~22년 차량요반도체 쇼티지 및 DB하이텍 실적 참고).

15인치(450mm) 웨이퍼 개발에 대한 이야기가 가끔 들리는데, 현실적으로 어렵다는 이야기가 많다. 아무래도 12인치 위주로 소부장 및 기술들이 자리를 잡았고 현재 12인치 미세화가 반도체 공정의 주요 쟁점이기 때문이다.

3) 반도체 전방 제품에 대해

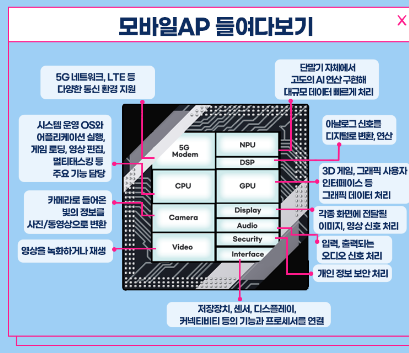

모바일: 일반PC에 뒤쳐지지 않는 퍼포먼스를 목표 삼는 동시에 크기 및 전력에도 신경써야 하는 까다로운 제품이다. 단순한 기능을 하는 값싼 반도체(센서)도 있기 때문에 세세히 보기는 어렵지만, 대표적으로 AP, DDI, PMIC, CIS, SIM, 자이로센서, 터치컨트롤러 등이 탑재된다. 전세계 스마트폰 출하량은 연 12~14억대로, 인구 수에 비례하므로 중국/인도 비중이 크다. 수요가 정체된 시장으로 공급단에서 스펙을 늘리는 방향으로 성장을 이끌어내고 있다.

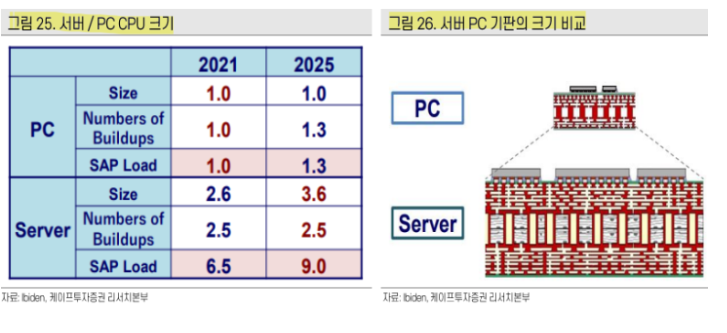

PC: 1990년대 개인컴퓨터 시대가 열리면서 반도체에 대한 개념을 일반인에게 심어다준 제품이다. HPC나 서버에 들어가는 반도체를 만드는 기업들은 대부분 PC시장에서 기반을 쌓았다. 서버 시장이 커지기 전에는 CPU, GPU, DRAM, SSD의 성장 동력이 PC시장이었다. 전세계 PC 출하량은 연 2.5~3억대 정도로, 수요가 정체된 시장이다.

HPC: HPC는 슈퍼컴퓨터의 약자로 진정한 계산만을 위해 만들어진 컴퓨터다. HPC의 주요 프로세서는 다음과 같이 발전했다. 전용CPU 1개 > CPU 병렬사용 모바일> 저전력 CPU 다수 > CPU+GPU. 2010년대 들어서면서 GPU를 도입했는데, 아직까지는 기계학습과 관련하여 단순 반복 작업 위주로 사용되고 여전히 시스템 총괄 및 관리는 CPU가 담당하고 있다. HPC는 선진국 대부분이 자체적으로 보유하고 있지만, 자본력이 있는 기업들도 본인들 사업과 시너지를 내기위해 구축하고 있다.

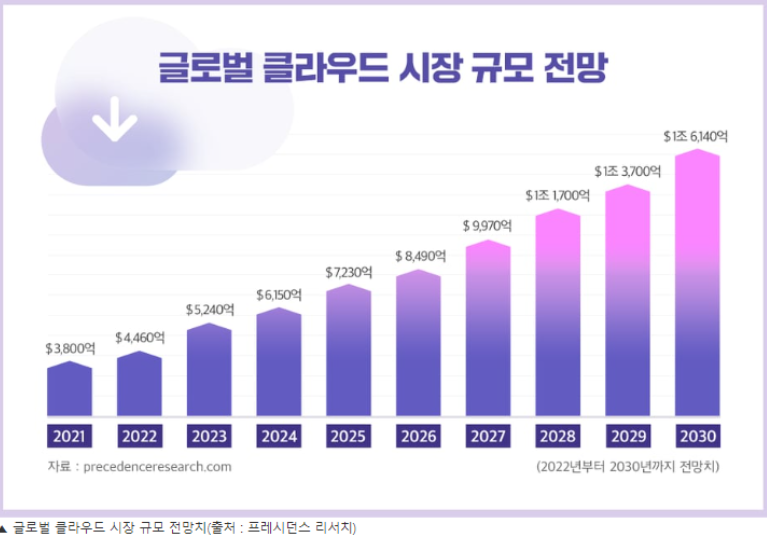

데이터센터(IDC): 인터넷과 연결된 데이터를 모아두는 시설이다. 흔히 말하는 서버나 클라우드의 물리적 공간이 데이터센터라고 보면 된다. 빅테크기업들이 거대자본으로 데이터센터를 구축하고 클라우드 서비스를 통해 B2C를 넘어 B2B로 온라인 임대를 해주고 있는 격이다.

전장: 자동차는 제조업의 꽃이다. 기존에는 수많은 센서와 MCU로 이루어져 있었는데, 자율주행 기술이 발전하면서 성능이 뛰어난 중앙제어칩 및 디테일한 반도체에 대한 수요가 늘고 있다. 일반적인 내연기관차에 반도체가 300~500개 들어가는 반면, 자율주행 전기차에는 2000개 정도가 들어갈 것이라고 한다.

1.2 메모리

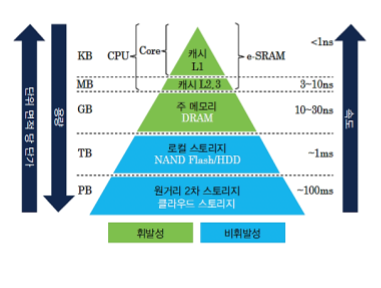

메모리 반도체는 정보의 저장을 위해 만들어진 반도체로, 크게 휘발성 메모리와 비휘발성 메모리로 나뉜다. RAM이 대표적인 휘발성메모리로 정보를 임시저장하고, 낸드플래시(NAND FLASH)가 대표적인 비휘발성메모리로 정보를 영구저장한다.

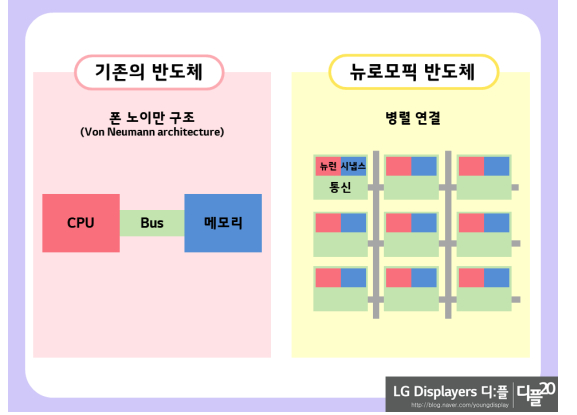

다양한 메모리들은 위와 같이 계층이 나뉘는데, 폰노이만 구조가 일반적인 현재 컴퓨팅 시스템에서는 병목현상을 해결하기 위해 로직반도체와-스토리지 사이에 성능 차이를 줄이는 노력을 하고 있다. 그로 인해 위와 같은 다양한 스펙의 메모리 반도체들이 주기억 부터 보조기억 까지 줄지어 나란히 연결되게 된다.

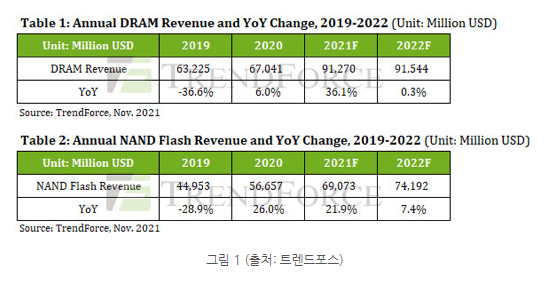

하지만 사실상 D램과 낸드플래시가 메모리 시장을 이끌고 있으며, 그러한 메모리 반도체 시장은 전체 반도체 시장 대비 20~30%를 차지하고 있다. 그러하여 본 항목에서는 D램과 낸드플래시에 대해서 중점적으로 다루고자 한다.

D램과 낸드플래시의 시장 크기는 다음과 같다.

1) D램 기초

대표적인 주기억장치 역할을 하는 메모리 반도체이다. D램은 셀 단위로 이루어지는데, 1셀에 1개의 캐패시터와 1개의 트랜지스터가 있다. D램은 용량도 용량이지만, 직접적인 성능 평가는 레이턴시/대역폭으로 비교된다.

참고로, 원천기술이 IBM에게 있기 때문에 D램을 제조하는 업체들은 IBM에게 매번 특허 사용료를 지불하고 있다.

다음은 국제적으로(JEDEC) 표준화된 D램의 형태들이다. .D램은 비동기식과 동기식으로 나뉘는데, 현재 쓰고 있는 대부분의 D램은 동기식 D램으로 풀 명칭은 SDRAM이다.

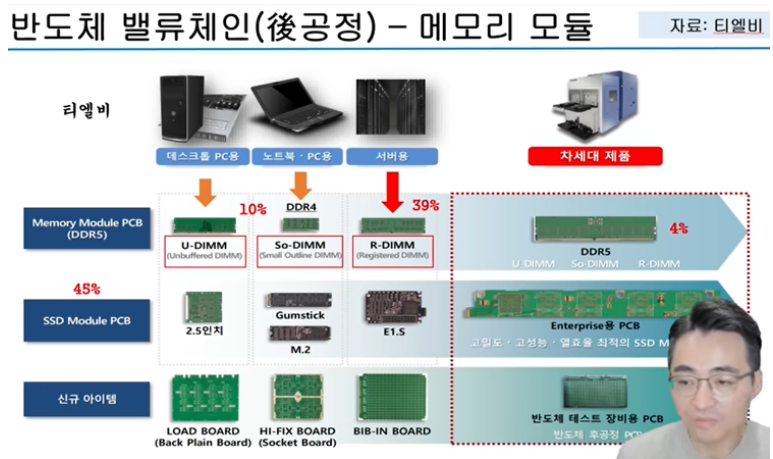

DDR: DDR SDRAM. 기존 SDRAM보다 데이터 처리율이 2배인 D램. CPU/GPU/메인보드에 따라 호환되는 DDR세대가 다르다. 그래서 D램만의 세대변화로만 시장을 이끌 수 없다. 보통은 소비자들이 CPU와 GPU의 스펙을 보고 반도체 구매를 나서기 때문에, CPU와 GPU가 몇 세대의 DDR을 호환하느냐가 D램 시장에 큰 영향을 끼친다.

UDIMM: 데스크탑용 RAM 모듈. DDR세대별로 TYPE이 달라진다.

SO-DIMM: 중소형 기기 RAM 모듈. DDR세대별로 TYPE이 달라진다.

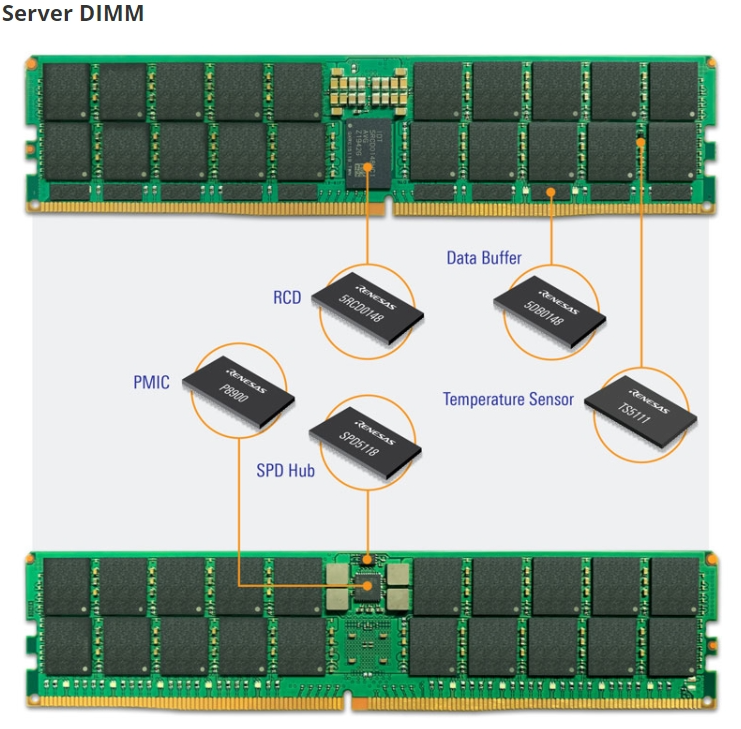

R/LR-DIMM: 서버용 RAM 모듈. 타 모듈대비 많은 RAM을 실장할 수 있다. DDR세대별로 TYPE이 달라진다.

LPDDR: Low Power DDR. 기존 모바일 DDR로 불렸던 저발열/저전력 버전의 D램. 2023년 LPDDR5X가 최신시리즈다.

GDDR: Graphics DDR. 그래픽 처리에 특화되어 GPU와 같이 실장되는 메모리. 2020년 GDDR6X가 최신시리즈다. 비용이 높아 고성능 GPU나 콘솔용에 주로 쓰였는데, HBM의 등장으로 포지션이 애매해졌다.

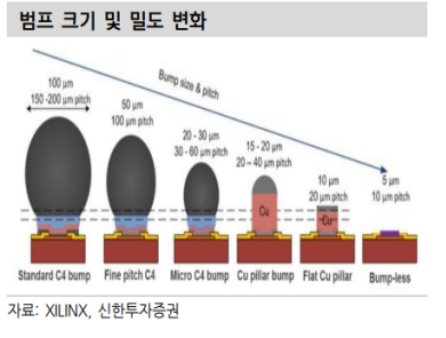

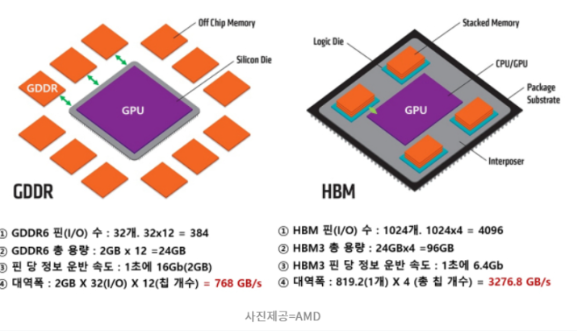

HBM: 로직반도체와 같이 인터포저에 패키징하며 D램을 수직적층한 칩. 고대역폭을 지원하며 TSV와 마이크로 범퍼로 연결한다. 현재는 AI와 HPC에 GPU가 대거 들어가면서 HBM이 고성능 GPU와 세트로 된 느낌이 크다.

HBM-PIM: PIM에 HBM을 탑재한 칩. PIM은 Processing in Memory로, 메모리 내부에 연산 능력이 있는 프로레서를 더한 융합기술을 의미한다. 로직반도체를 대신하는 것이 아닌, 병목현상을 줄여주고 가속기 역할을 하는 메모리 반도체라고 보면 된다.

3D-DRAM: 차세대 메모리. 5.6항목에 정리.

CXL D램: 차세대 메모리. 고성능 연산이 필요한 어플리케이션(AI, HPC)에서 서로 다른 기종의 제품들을 효율적으로 연결할 수 있는 차세대 인터페이스를 위한 메모리. HOST가 되는 메인메모리와 함께 활용될 수 있도록 용량/대역폭을 확장한다. 기존에는 CPU 하나당 512GB D램 모듈을 16개 꽃아서 8TB가 최대였는데, CXL 인터페이스 사용시 32개를 꽂아 16TB까지 확장 가능하다(삼전기준).

어플리케이션별 시장 상황은 다음과 같다. 비중은 유닛의 비중을 말하는 거고, 사실상 비트의 크기가 중요하다.

모바일: 비중 약 30%. 비트로는 6만 MGB 예상. 모바일 시장 자체가 중국 비중(30%)이 크기 때문에, 중국의 D스마트폰 시장이 중요하다.

PC: 비중 약 15%. 비트로는 3만 MGB 예상.

서버: 비중 약 40%. 비트로는 5만 MGB 예상. D램은 서버 CAPEX에서 25% 정도를 차지할 정도로 매우 큰 역할을 한다. 서버향은 PC용 대비 20~30% 단가가 높다.

기타컨슈머: 비중 약 6%. 비트로는 300MGB 예상(탑재용량이 워낙 작기에). 스마트워치나 XR기기와 같은 기타 IT기기들 포함.

전장: 매우 미미.

2) D램 주요 포인트

용량의 증가: 현재 단일 칩 최대용량은 DDR5 64GB이다. 보통 주력모델은 최대의 절반이다(32GB).

D램의 미세화: D램도 미세화를 진행하고 있는데, 현재는 10나노대에 머물러있다. D램의 공정은 다음과 같이 구분한다.

|

공정 로드맵 |

1x |

1y |

1z |

1a (현재 메인) |

1b |

1c |

|

미세화 |

19~18nm |

17~416nm |

15nm |

14nm |

13~12nm |

11nm |

|

EUV도입 |

|

|

삼전 |

SKH |

|

마이크론 |

캐패시터의 변화: 반도체가 미세화되면서 캐패시터의 면적이 작아지고 있다. 그러면서 키가 커지고 종횡비가 높아지면서 무너지는 현상이 발생한다. 이 현상이 D램 미세화의 숙제다. 현재 거론되는 해결방안은 '더블필러' 및 '새로운 High-k물질' 이다. High-k물질에 대해서는 '5.2항목 HKMG'에서 자세히 보겠지만, D램 캐피시터에 제일 많이 쓰이는 High-k는 지르코늄이다. 정확히는 지르코늄에 Al2O3를 결합해서 만든 ZAZ구조이다. 현재는 1a 공정이 많이 쓰이면서 하프늄을 도입했고, 유전율이 더 높은 TiO2를 도입하려는 노력을 하고 있다.

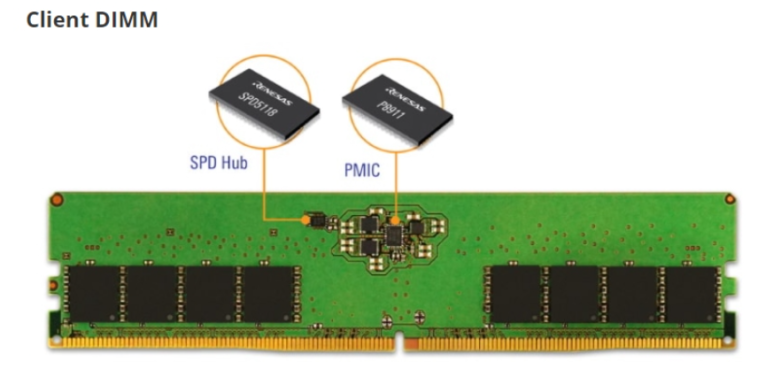

DDR5: 5세대 DDR이다. 성능의 향상은 다음 영상을 참고하면 되고 특이점이라 하면, 기존에 메인보드에 실장되었던 PMIC가 D램 모듈에 실장되는 것이다. 이렇게 되면, 기존에 메인보드 패키징 업체에서 정하던 PMIC를 D램업체가 정할 수 있게 되고 PMIC를 제조하는 삼전 입장에서는 긍정적인 효과를 볼 수 있다(그래봤자 8인치 반도체 ㅎ). DDR5의 생산은 14nm이하의 공정에서 진행되어 이미 D램업체들이 제조능력을 갖췄음에도 불구하고, 호환되는 서버용 CPU(인텔의 사파이어래피즈)가 출시지연 되면서 출하를 하지 못했다(PC용 DDR5는 21년 인텔의 엘더레이크가 출시되면서 시판되었다). 서버용 DDR5가 계속해서 자리를 잡지 못하고 있는데, 2H23에 데이터센터 투자가 일어나면서 수요가 늘어날 것으로 보고 있다.

PC용 DDR5와 서버용 DDR5

HBM: 5.5항목에 정리.

3D-DRAM: 5.6항목에 정리.

3) NAND 기초

전원을 끄면 데이터가 사라지는 D램, S램과 달리 정보를 영구적으로 저장한다. 어플리케이션에 따라 여러가지 모듈로 나뉘는데, 대표적인 것이 SSD다.

MMC: 멀티미디어카드. SD카드에 의해 사장되었다.

(마이크로)SD카드: SSD와 다르게 컨트롤러가 필요 없다. 그래서 성능이 비교적 낮다.

eMMC: 임베디드 기기를 위해 나온 MMC. 내장형이기 때문에 마더보드에 직접 납땜된다. SSD 대비 용량이나 속도면에서 낮지만 비교적 저렴하여 저성능 소형기기부터 치고 올라왔다. 주로 보급형 스마트폰/노트북에 쓰인다.

UFS: eMMC의 후계자로, eMMC의 어플리케이션들을 침투하고 있다. 주로 플래그십 스마트폰/노트북에 쓰인다.

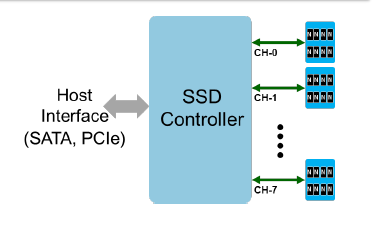

SSD: 메모리 반도체를 저장매체로 사용하는 고속 저장장치. 컨트롤러/낸드플래시/D램으로 구성되어 있다. 여기서 컨트롤러는 비메모리반도체로 SSD의 성능을 좌지우지한다.

SATA방식: 기존에 쓰이던 통신 방식.

NVMe방식: PCle버스를 통해 작동하여 램과 비슷한 특성을 지닌 통신 방식. SATA방식 대비 대역폭이 높다.

*애플은 로직반도체에 직접 낸드 컨트롤러를 심어두고, 낸드만 받아서 탑재한다. 남 줄거를 하나라도 줄인다. 대단하다.

어플리케이션별 시장 상황은 다음과 같다.

모바일: 비중 약 40%. 비트로는 40만 MGB. 데이터 처리량 증가로 비트는 늘어날 것으로 예상.

PC(cSSD): 비중 약 22%. 비트로는 30만 MGB. 시장 자체는 커지지 않았지만, PC의 SSD 채택 증가율이 급상승하여 다른 어플리케이션 대비 최근 몇년간 제일 빠른 성장을 보였다.

서버(eSSD): 비중 약 22%. 비트로는 16만 MGB. 하이엔드 컨트롤러가 필요해서 고부가가치 제품이다. 아직까지는 HDD 대비 가격이 8배 정도 높아 시장 침투율이 낮다(15%). 단순 데이터 저장은 HDD에, 접근 빈도가 높은 컴퓨팅 데이터는 SSD로 채택하는 추세다.

외장메모리: 비중 약 13%. 비트로는 10만 MGB. 플래시메모리나 USB같은 메모리.

전장: 비중 약 2%. 비트로는 4000 MGB.

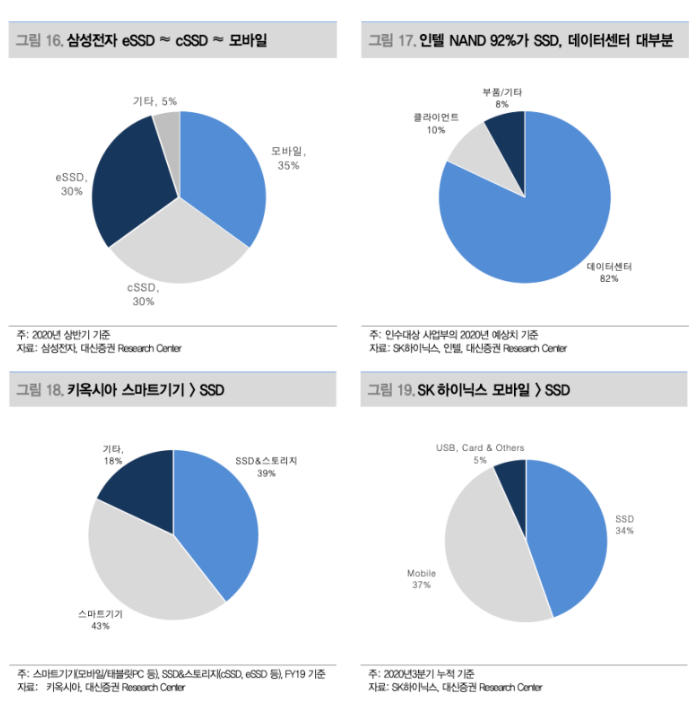

낸드 시장이 D램 시장과 크게 다른 점이라면, 디램은 대형 3사가 어플리케이션별로 비슷한 비중을 두지만 낸드는 업체별로 주요 어플리케이션이 다르다는 것이다 (모바일은 D램과 낸드를 세트로 팔기 때문에, D램이 없는 낸드업체는 모바일 비중이 낮음-키옥시아 예외).

4) NAND 주요 포인트

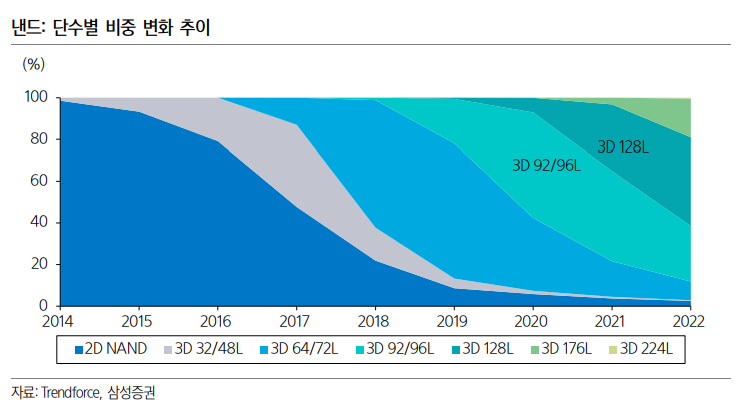

3D NAND(VNAND): 메모리 반도체 역할 상 '저장'에 포커싱이 되있기 때문에 셀을 늘리는 것이 포인트다. 옆으로 늘리는 것보다 위로 늘리는게 비용면에서 훨씬 효율적이기 때문에 미세화보다 고단화에 중점을 두게 되었다. 그렇다보니 낸드에서 선단은 노광을 통한 미세화가 아니라, 증착과 식각을 통한 고단화이다.

더블스태킹: 3D낸드가 고단화되면서 한번에 깊은 홀을 뚫기가 어려워졌다. 그러하여 쌓고자 하는 층수의 절반을 나눠 따로따로 적층 후 합치는 것이다. 공정은 쉬워지지만 비용은 크게 늘어난다. 업체마다 더블스태킹을 적용한 시점은 다 다르다.

원가경쟁: 낸드플래시는 D램에 비해 중견업체가 아직 많으며, 품질 차이도 그렇게 크지 않다. 그래서 원가경쟁력이 낸드플래시 시장의 핵심이라고 볼 수 있다.

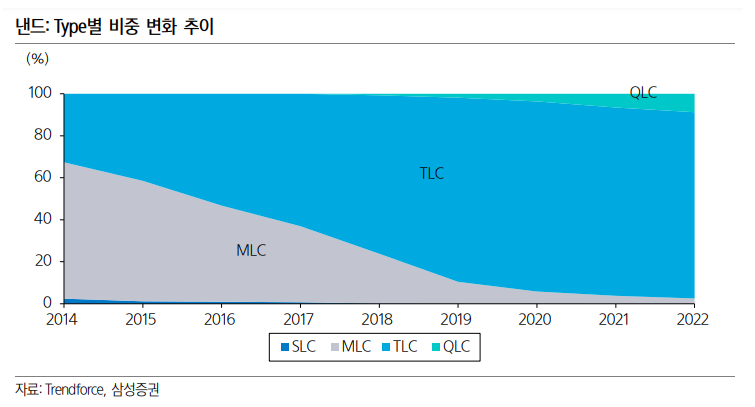

TLC, MLC, QLC: 기존에는 한 셀에 1비트가 저장되어 데이터를 2가지 저장할 수 있었는데, 전압차이를 통해 1셀에 4비트까지 저장할 수 있게 한 것. QLC로 갈수록 단가 당 저장용량은 올라가나 데이터 손실확률이 높아진다.

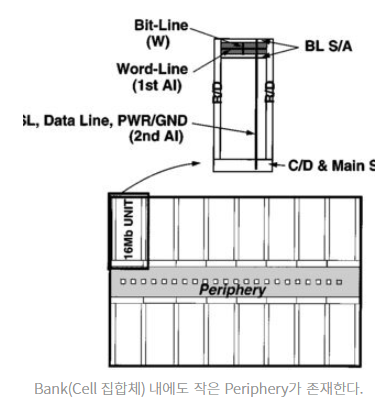

4D NAND(하닉): COP(삼전), PUC(마이크론) 등 제조사별로 부르는 용어가 다르다. 낸드에서 전압제어를 담당하는 periphery라는 주변회로를, 메인회로에 넣어 같이 적층시키는 것이다. peri를 하부에 넣고 상부기판을 넣은다음 셀을 적층하는 구조인데, 상부와 하부를 연결하기 위해 via관통기술이 필요하다.

5) S램

메모리 반도체 중 속도가 제일 빠른 반도체로, 휘발성 메모리다. 제일 빠르지만 회로가 복잡하여 집적도가 낮고 비싸서 대용량 제조가 어렵다. 그래서 폰노이만 구조에서 로직반도체에 제일 가까운 캐쉬메모리에 주로 쓰인다. 캐쉬메모리는 로직반도체에 내장되어 있다.

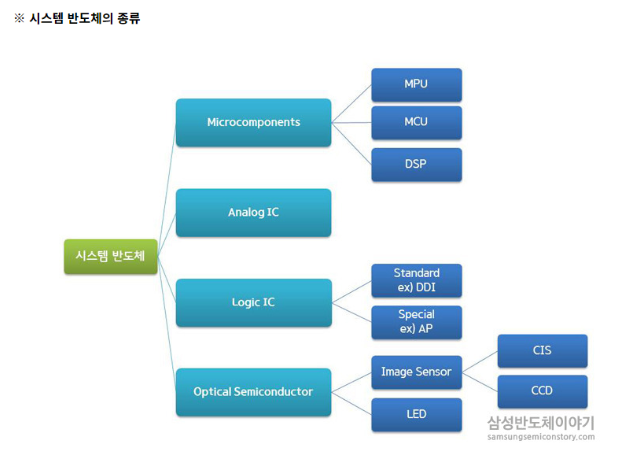

1.3 비메모리

비메모리 반도체는 시스템 반도체라고 부르기도 하지만, 사실 공통된 특징을 가진 반도체를 지칭하는 표현이 아니다. 메모리에 해당하는 반도체를 제외하는 모든 반도체를 비메모리라고 하는 것이기 때문에, 비메모리에 대해 이야기를 하려면 여러가지 범주로 나눠서 이야기 해야한다.

대표적인 비메모리 반도체가 CPU, GPU, ASIC, 센서이다. 다음은 반도체 품목별 시장 규모이다.

※비메모리 반도체의 범주

먼저, 비메모리 반도체는 크게 아날로그 반도체와 디지털 반도체로 나뉜다. 반도체를 생각하면, 디지털이라는 단어가 왠지 적합해보이며 우리가 아는 반도체는 대부분 디지털이지만, 아날로그 반도체는 알게 모르게 일상생활 곳곳에 많이 쓰인다.

아날로그 반도체는 생활 속의 아날로그 신호(소리, 빛 등)를 디지털 신호로 바꾸거나 그 반대로 바꾸는 반도체이다. 그래서 이러한 개념 때문에 위 그림은 아날로그IC를 따로 구분했지만, 사실 로직반도체와 MCU가 아닌 대부분의 비메모리반도체를 아날로그 반도체로 이야기한다. 아날로그 반도체는 대부분 비용 대비 성능을, 올릴 만큼 올린 레거시 제품으로(미세화에서 성능을 뽑아내기도 힘듦), 8인치 웨이퍼 팹에서 제조되어 단가가 그렇게 높지않다 (반대로, 8인치팹은 증설하기가 쉽지 않아서 폭발적인 수요가 일어나면 쇼티지가 오래간다).

디지털 반도체를 보면, 로직반도체가 대표적인 디지털 반도체다. 로직반도체는 and나 or등 로직을 이용해서 연산을 처리하는 반도체다. 우리가 잘 아는 CPU, GPU, ASIC, FPGA, AP가 로직반도체인데, 서로가 시장을 침투하기 보다는 각각의 쓰임이 다르다고 보면 된다. 그렇기 때문에 시대를 주름 잡는 어플리케이션이 무엇이냐에 따라 특정 로직반도체만 수혜를 받기도 한다.

2000년대까지는 모든 비메모리 반도체 사양이 그렇게 높지 않았기 때문에, 당연히 단일 수행능력이 뛰어난 CPU가 주목을 받았다. 그때 인텔은 '반도체의 절대신'이었다. 2010년대는 대부분의 반도체 성능이 상향평준화되면서 빠른 처리가 중요하게 되었다. 특히 코인채굴, 고사양 그래픽에서 그러한 니즈가 생겼고 병렬처리에 특화된 GPU가 주목을 받았다. 당시 엔비디아의 GPU 중고가는 출고가보다 비싸게 팔리기도 했다.

최근에는 빅테크업체들이 디지털 트랜스포메이션을 이끌어가면서 머리를 굴리기 시작했다. "엔비디아하고 인텔 임마들 지나치게 고사양으로 만들어놓고 가격만 막 부르는거 아이가! 설계만 할 줄 알면 그그그 대만아들 하고 한국야들이 만들어준다카이" 하면서 자기들 어플리케이션에 맞게 직접 칩을 설계하기 시작했다. 그것이 ASIC(주문형반도체) 다.

1) CPU

컴퓨터의 대뇌라고 할 정도로 연산/기억/해석/제어에 큰 역할을 하는 반도체이다. 중앙처리장치라고 부르기도 한다.

※아키텍쳐: 반도체 칩을 만들때 각 소자들(코어나 캐시메모리 등)이 서로 효율적으로 호환되도록 하는 명령어 셋(소자들간의 언어) 및 물리적 설계 밑바탕이다. 반도체 간에 비교할 때 명령어 셋은 같을 수 있으나, 물리적 설계는 다를 수가 있다. 예를 들어, 인텔과 AMD의 CPU 둘다 명령어 셋은 x86-64를 사용하나, 물리적 설계를 보면 인텔은 000레이크, AMD는 젠이라는 명칭을 쓰는 것을 볼 수 있다. 다음은 로직반도체 시장을 이끌고 있는 대표적인 아키텍쳐들이다. 하지만 반도체 엔지니어가 아닌 이상 '아키텍쳐=물리적구현'으로 말하는게 보통이다.

인텔: 1970년대 32비트 전용 아키텍쳐인 x86개발.

AMD: 1990년대 64비트 전용 아키텍쳐인 AMD64개발. 인텔이 AMD64를 채택하면서 x86의 표준이 되고, 'x86-AMD64' 라고 부르게 된다.

ARM: 저전력에 초점을 맞춰 임베디드기기에 많이 쓰인다. 애플과 VLSI의 JV로 애플과 개인용컴퓨터 시장부터 협업을 많이 하다가, 스마트폰 시대로 넘어오면서 아이폰의 AP에 큰 기여를 했다. 대부분의 AP칩 뿐만 아니라,SoC칩들도 ARM아키텍쳐에 기반하여 설계되고 있다. AP칩에서 성공을 기반으로, 현재 서버시장 및 PC시장(애플의 M1)에서 확장을 진행하고 있다.

※MPU: 마이크로 프로세싱 유닛의 약자. CPU가 작게 만들었다고 해서 쓰인 용어인데, 현재의 CPU는 다 작기 때문에 동일어라고 생각하면 된다.

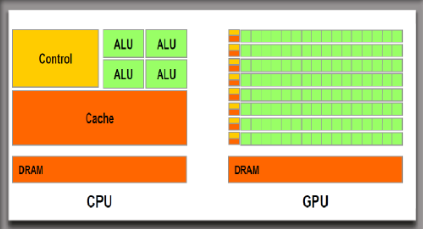

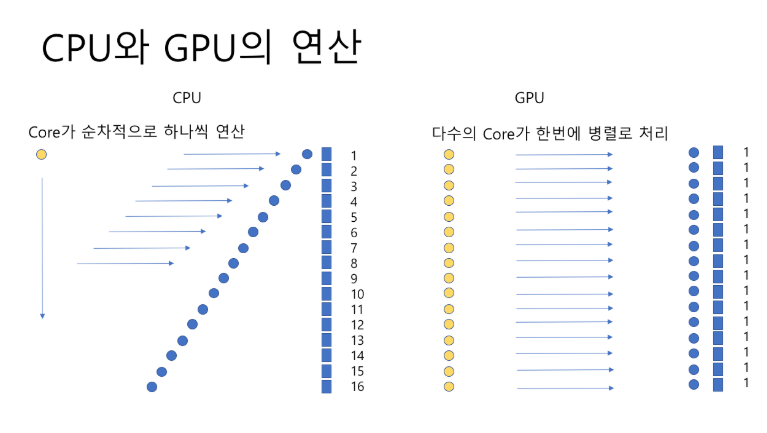

2) GPU

GPU는 그래픽 처리장치로, 게임/동영상 등 그래픽 연산에 특화된 칩이다. GPU는 그래픽 구현에 목적을 둔 칩인데. 코어가 수백개로 대규모 병렬연산 수행에 최적화 되어있어 가능하다. 병렬연산으로 빠른 연산능력이 가능한 것이고, 수많은 픽셀로 이뤄진 그래픽에 적합한 것이다 (CPU는 코어가 싱글단위지만, GPU의 코어보다 훨씬 복잡하다).

CPU와 GPU의 차 (출처-https://blog.naver.com/sjc02183/221692078882)

2010년대 초반까지만 해도 'GPU=그래픽 처리장치' 라는 인식이 강했으며 GPU는 CPU의 간단한 작업을 빠르게 처리해주는 반도체로 취급받았다. 하지만 GPU의 선두주자인 엔비디아가 병렬연산의 장점을 활용해서 다양한 영역에 침투하여(GPGPU) 그 위상을 높이고 있다. 대표적인 것이 빅데이터, 시뮬레이션, 코인채굴, 딥러닝이라고 볼 수 있다.

※GPGPU: GPU를 활용하는 범용 다중연산장치. GPU의 상당한 연산능력을 이용해, GPU의 원래 주 활용도인 그래픽을 넘어 다른 연산에 쓰이는 것을 뜻하는 개념. 최근에 GPU의 활용도가 높아지면서 떠오르는 키워드인데, 너무 많이 활용되다보니 GPGPU=GPU 가 되어버렸다.

3) ASIC

기업의 입맛에 맞게 주문제작되는 반도체이다. 반도채의 전방인 전자기기 시장이 급속도로 변하는 과정에서, 각 어플리케이션별로 최적화된 칩을 만들기 위해 생긴 개념이다. 그렇기 때문에 특정 종류의 칩이 아니라, 여러가지 기능이 한번에 탑재되는 SoC칩의 형태를 띄는 경우가 많다. 대표적인 ASIC 칩들은 다음과 같다.

테슬라의 D1: 머신러닝을 위해 개발한 반도체다. 테슬라 자체 슈퍼컴퓨터인 도조에 들어가며, 엔비디아 A100보다 성능이 좋은 것으로 알려져 있다.

애플의 M시리즈: 애플의 자체 PC에 탑재하기 위한 반도체다. SoC형태로 CPU, GPU 및 NPU(Neural Engine)이 들어가 있다.

구글의 TPU: 구글이 딥러닝을 위해 개발한 맞춤형 AI가속기 반도체다. 현재 구글의 데이터 센터에서 여러 데이터들을 처리하는데 쓰이고 있다. AI시대를 맞이하면서 구글에서 새로운 반도체 종류로 브랜딩 하고 있는데, 타업체가 아직까지 채택하고 있지 않아서 사실상 ASIC로 구분된다.

※ NPU

인공 신경망 처리를 위해 만든 반도체이다. AI연산 학습(딥러닝, 머신러닝)에 최적화된 반도체다. 아직 시장 초기이기 때문에 AI엑셀레이터, TPU 등 다양하게 불리며, CPU/GPU를 보조하는 포지션으로 채용된다. 그리고 각 업체마다 설계가 다르기 때문에, ASIC 칩으로 분류된다고 볼 수 있다. 구글의 TPU, 아마존의 AWS Inferentia, 인텔의 NNP, 엔비디아의 NVDLA, 테슬라 FSD칩, 애플의 뉴럴엔진 등이 있다. 엔비디아 GPU에 들어가는 TENSOR CORE도 NPU라고 할 수 있다.

4) FPGA

설계 후 회로 변경이 불가능한 다른 반도체들과 달리, 용도에 맞게 프로그래밍하여 재설계 할 수 있는 반도체다. 사용자의 용도에 따라 변형시킬 수 있어, 변화가 급진적인 환경에 주로 쓰이고 있다. 또한 고성능 및 고가(재설계할때마다 돈이다)의 제품으로 AI, 첨단팹, 항공, 우주, 방산, 통신 등 한정적인 영역에 쓰인다.

FPGA는 다른 칩과의 호환성이 좋아, 로직반도체와 같이 실장되기도 한다. 인텔이 알테라를, AMD가 자일링스를 인수한 배경도 거기에 있다.

앞서 말했다시피, FPGA는 변화가 급진적인 환경에 주로 쓰이지만, 그러한 곳들은 대량 수요가 잘 없고, 대량 수요가 있더라도 직접 설계하여 ASIC를 발주하는게 효율적이기 때문에 FPGA의 단독 시장 자체는 크지 않다고 볼 수 있다. 오히려 ASIC를 주문하기 전에 FPGA를 테스트 용도 쓰는 곳이 많다.

5) AP

Application Processor. 대표적인 SoC반도체다. 하나의 칩 안에 CPU, GPU, NPU, RAM, 컨트롤러 등이 들어가 있는 반도체로, 스마트폰 내 모든 명령을 처리한다. PC본체에 들어있는 반도체들와 컨트롤러들을 소형 어플리케이션인 스마트폰에 넣다보니, 전력/크기에 중점을 맞춰 설계된 칩이라고 보면 된다.

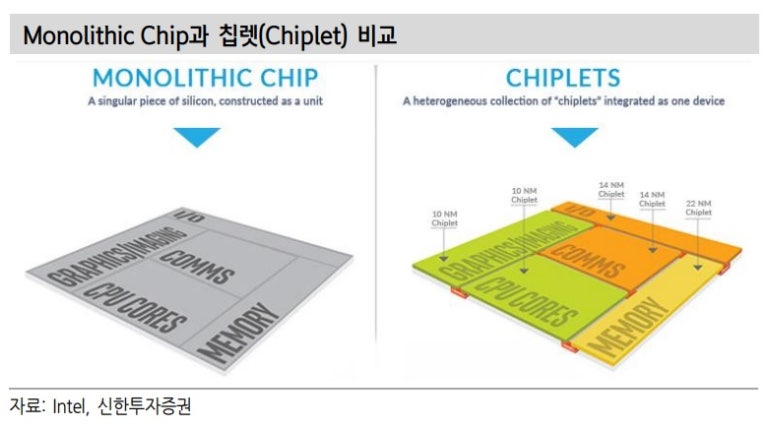

※SoC칩: System on Chip. 반도체 칩 하나에 여러 기능을 하는 회로가 새겨진 것이다. 반도체 후공정의 패키지 공법인 SiP와 헷갈리기 쉽다. SiP는 전공정이 끝난 반도체칩을 모아서 후공정단에서 한개로 만드는 것이고, SoC는 전공정단에서 반도체 다이 하나에 여러가지 기능을 몰아넣는 것이다. 미세화공정이 진행될수록 SoC 비용이 기하급수적으로 오르고 수율이 낮아지면서, 크기에 제약이 없으면 단일칩으로 만들고 후공정에서 보완하는 추세다(5.3어드밴스드 패키징 항목 참고).

6) RF(RFIC)

모뎀칩에서 나오는 디지털 신호를 아날로그로 변환해 우리가 사용할 수 있는 무선 주파수로 바꿔주고, 반대로 모뎀칩으로 전송하기도 하는 무선 주파수 송수신 반도체다. 통신과 관련된 곳에 쓰이며, 스마트폰에도 들어가기 때문에 스마트폰의 성장과 함께 했다.

아날로그 반도체라 미세공정을 잘 도입하지 않는데, 삼전파운드리에서 8나노를 도입하는 것이 주목할만하다.

7) 모뎀칩

단말기(스마트폰, PC, IoT 등등)의 음성/데이터 정보를 이동통신 표준에 따라 신호로 바꾸는 반도체다. 퀄컴이 표준필수특허를 보유하고 있어, 이 칩셋을 이용하면 단말기의 일정 비율을 로열티로 지불해야한다.

이러한 퀄컴 독재체제에 불만이 있던 삼전/화웨이/애플은 자체 모뎀칩 특허 및 설계 역량을 키웠고, 현재까지 그 싸움이 이어지고 있다. 애플은 인텔의 모뎀사업부(only 스마트폰 모뎀칩)를 인수하고, 삼전은 자체 AP칩인 엑시노스에 자체 5G모뎀칩을 통합했다. 하지만, 애플은 개발에 실패했고 삼전은 자체 AP칩에 실패하고 스냅드래곤(퀄컴의 AP)을 채택하면서 그 꿈을 이루지 못했다.

8) MCU

마이크로컨트롤러의 약자로, 마이크로컴포넌트의 한 종류고 하나의 칩에 CPU/메모리/입출력장치가 통합되어있는 집적회로다. 하나의 칩에 다수의 기능을 담는 반도체이다보니, 사용처가 다양하고 간단한 전자제품들의 두뇌로 많이 쓰인다. 가전제품, 자동차의 간단한 기능을 하는 부분 등에 쓰이고 같은 전자제품군이라 하더라도 기능이 다양하기 때문에 주문 받아 제작하는 다품종 소량 생산 반도체다.

전자제품군의 발전과 함께해왔기 때문에 여전히 레거시 제품이 많이 있고, 안정성이나 더 나은 퍼포먼스에 대한 수요가 작기 때문에 레거시 제품의 비중이 크다. 대부분이 저가제품이라고 보면 되고 박리다매 반도체다. 2020년에 차량의 전동화가 일어나면서 차량용MCU 수요가 폭발적으로 증가했다.

9) DDI

디스플레이의 픽셀들을 구동시키는 반도체다. 픽셀에게 직접 명령을 내리지 않고 패널 안에 있는 TFT를 통해서 제어한다. 디스플레이에 나타날 것들을 본체(로직반도체)가 보내면 DDI가 통로 역할을 한다고 보면 된다.

DDI는 크게 2가지 시장으로 나뉘며, 사이즈가 클수록 DDI도 여러개가 들어간다.

Small DDI: 모바일 디스플레이향

Large DDI: 태블릿/PC/TV 디스플레이향

최근에는 OLED 시장이 커지면서 OLED DDI가 주목받고 있다.

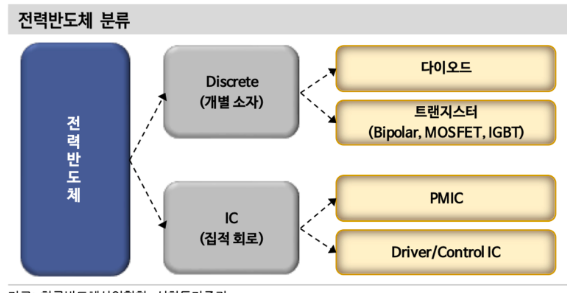

10) 전력반도체

전력반도체는 아날로그 반도체의 일종으로 전자기기에서 요구하는 전력/전압/전류 제어를 담당하는 반도체다. 전력반도체는 개별소자와 IC로 나뉘는데, 개별소자는 단순 기능을 담당하는 반도체고, IC는 개별소자를 한개의 칩 속에 집적시킨 반도체라고 보면 된다. 개별소자는 범용화된 제품이 많고, IC는 커스터마이징된 제품이다.

'전력반도체=PMIC'라고 헷갈리기 쉬운데, 전력반도체와 PMIC는 다른 용어다, PMIC는 전력반도체의 한 종류로, 전력관리반도체라고 부른다. PMIC는, 하나의 디바이스에 다양한 스펙의 부품들이 들어가기에 통합적으로 각각에 필요한 전압/전류를 보내줘 전력(배터리)을 효율적으로 쓰게 하는 반도체라고 볼 수 있다. 대표적인 사용처는 인버터, 컨버터, 전력인프라, 가전, 자동차가 있다.

전력반도체는 회로가 단순하고 레거시 제품이다 보니 싸게 만드는 것이 중요하다(적게는 1불도 안되며, 최대 5불 이라고 한다). 최근에는 서버/전기차/신재생에너지와 관련하여 고전압/고주파에서 물리적 특성이 우수한 반도체에 대한 니즈가 늘어나고 있다. 대표적인 그러한 반도체가 GaN과 SiC반도체(아직까지는 개별소자 단계)다. 이에 대해서는 5.4 항목에 정리하였다.

11) MMIC

마이크로파 대역의 회로를 집적시킨 고주파 반도체이다.안테나 신호의 송수신 역할을 담당하는 구성품인 송수신 모듈에 적용되고 있다. 주로 국방, 우주항공에 쓰인다. 국방, 우주항공은 고성능 제품이 필요하다보니 GaN, GaAs 등 화합물 반도체가 쓰인다. 통신용 반도체이다 보니 보통 RF를 다루는 기업에서 주로 제조한다.

12) CIS(CMOS 이미지센서)

피사체 정보를 읽어 빛을 전기신호로 변환해주는 반도체이다. 우리가 아는 디지털성 카메라에는 다 들어간다고 보면 된다. 일반 반도체 공정으로 쓰이는 CMOS 공정을 이용하여 제조하며, Si로 epi층을 만든 특수 웨이퍼를 사용한다.

CIS에서는 트랜지스터보다 포토다이오드 소자가 핵심이며, RGB간에 빛 간섭을 줄이는 것이 주요 포인트다. 그러기 위해서는 isolaton 구조가 중요한데, CIS선두주자인 소니와 삼전은 이를 위해 Trench방식을 채택했다(이것이 삼전의 ISOCell).

참고로, CIS는 다음과 같이 크게 두 가지 기술로 진화하고 있따.

FSI: 웨이퍼에 포토 다이오드를 만들고 그 위에 트랜지스터와 배선을 올리는 구조. 트랜지스터 때문에 포토다이오드의 면적이 줄어들어 잘 사용하지 않는다.

BSI: 트랜지스터와 포토다이오스를 웨이퍼 서로 반대쪽으로 배치한 구조. 여기서 더 나아가, 트랜지스터와 웨이퍼를 증착하는 Stack CIS구조가 있다.

13) LED

발광다이오드라고 하며, 2종 이상의 원소로 이뤄진 화합물 반도체다. 주로 GaAs(갈륨비소), GaP(갈륨인), GaN(갈륨질소) 등으로 만들어진다. 전기에너지를 빛에너지로 변화해주는 광반도체라고도 한다. 다른 발광물체(LCD 등)들 대비 전력소모가 적고, 반도체 소자라서 제어하기가 쉽다.

14) 낸드 컨트롤러

본체와 교신하여, 낸드플래시 제품(ex-SSD) 안에 탑재된 다수의 낸드플래시들을 선택하여 어디에 저장할지, 어떻게 관리할지 컨트롤하는 비메모리 반도체다. 낸드플래시 자체도 중요하지만, SSD컨트롤러의 성능에 따라 SSD가 좌지우지되기도 한다. 하이엔드제품 제조 기업에 삼전, 마벨이 있고, 인텔과 도시바는 마벨과 협력하여 자사 제품을 만들었다. 저가형으로는 파이슨, 실리콘모션 제품이 있다.

삼전만 유일하게 자사 메모리반도체에 자사 컨트롤러를 탑재하는 인하우스 강자이다. 낸드용 컨트롤러도 싱글나노 공정에서 이뤄지는 하이엔드 제품으로, 설계 및 제조가 어렵기 때문이다.

1.4 반도체 기업의 세분화

각 항목의 대표적인 기업들은 2편에 정리했다.

1) IDM(종합 반도체 기업)

반도체 생산에 관련된 모든 공정(설계/생산/패키징/테스트~)을 수행하는 기업이다. 반도체 팹에는 막대한 자금이, 설계에는 우수한 인재가 필요하므로 글로벌로 대형 IDM 업체가 많지 않다. 또한 IDM 업체라고 해도 부분부분에서 외주를 주거나 공정별로 전담업체를 정하여 생태계를 형성하기도 한다.

2) 팹리스

말 그대로 팹(FAB)이 없는 기업으로, 반도체의 설계와 개발만을 전문으로 하는 회사이다. R&D 영역이 해자가 되므로 연구인력이 대단히 중요하다고 볼 수 있다. 다만, 팹이 없어 규모의 경제를 실현할 수 없으므로 우수한 IP와 인력만 있으면 침범이 가능한 영역이다. 실제로, 2010년대 후반부터 다양한 빅테크 기업들이 본인들 입맛에 맞도록 칩을 설계하며 팹리스 시장에 뛰어들고 있다.

3) 파운드리

반도체 제조를 전담하는 생산 전문 기업이다. 반도체 설계 디자인을 전문으로 하는 기업으로부터 제조를 위탁받아 반도체를 생산하는 기업이라고 보면 된다.

반도체 팹은 특성 상 인프라 및 장비 구축에 있어 막대한 규모가 들기 때문에 신규 진입이 쉽지 않은 편이다.

다른 제조업의 ODM, OEM과는 개념이 아예 다르다. 제조를 맡긴다는 개념이 아닌, 반도체 칩 제조과정의 전반을 관리한다는 개념이다. 실제로 팹리스가 직접 공정 설계도를 짜고 OSAT업체 찾아다니며 반도체 칩이 나오기까지를 감독하기가 쉽지 않기 때문에, (생태계 형성을 통해) 턴키로 해주는 파운드리는 팹리스에게 매력적일 수 밖에 없다.

4) 디자인 하우스

팹리스가 파운드리에 위탁 할때, 파운드리 생산에 최적화 되게끔 재설계 해주는 기업이다. 아무래도 팹리스 기업 자체에서 직접하는 경우가 많기 때문에, 팹리스와 디자인하우스의 구분이 뚜렷하지는 않다.

규모가 큰 디자인 하우스는 대부분 대형 파운드리업체와 협력하는 경우가 많다. 이를 DSP(디자인솔루션파트너)라고 하며, 파운드리 생태계에 있어 중요한 부분이다. 이 디자인 하우스가 일을 잘해야, 반도체를 한번도 만들어보지 않는 거대자본들이 자기들도 팹리스 할거라고 찾아오기 때문이다.

국내 디자인하우스는 주로 후공정의 설계를 담당하는 경우가 많다.

5) 칩리스(IP 및 EDA)

말 그대로 자사의 칩이 없는 기업으로, 반도체 설계에 있어 필요한 IP 및 TOOL(EDA)만 다루는 기업이다. 칩리스는 설계 라이센스를 판매하여 라이센스 제공에 따른 로열티가 주 수입원이다.

반도체에서 IP는 보통 설계에 필요한 블럭(코어, 셀라이브러리)을 말하는데, 반도체 회로를 구성함에 있어 자주 사용하는 블럭은 직접 설계하기보다 이미 설계된 블럭을 가져오는게 효율적이다.

그리고 EDA(Electronic Design Automation)는 반도체 설계/검증/수율향상에 사용되는 각종 자동화된 설계도구를 의미한다. EDA TOOL은 소프트웨어마다 보통 1~2억원이며, 팹리스는 칩 개발 시 보통 10여종 이상의 TOOL을 사용한다.

6) 소재 기업

반도체 제조 공정에 필요한 각종 전구체, 케미칼 등을 다루는 기업이다. 장비 기업에 어느 정도 종속된 부품기업들과는 다르게, 반도체 팹의 조건만 충족시키고 원가절감을 이루는 업체에게 해자가 있다고 볼 수 있다. 소재는 한번 납품하기 시작하면 지속적으로 계속 쓰이기 때문에 하향사이클을 잘 타지 않는다.

물론 소재는 기초화학 연구능력과 원자재의 비중이 크기 때문에, 한국에서는 쉽지 않은 BM이다.

7) 부품 기업

대부분, 공정의 메인 장비에 들어가는 부품을 제조하는 기업이다. 장비기업에 종속되어 장비 납품시 매출 성장이 일어나는 비포마켓과 장비 납품 후 추후 관리에서 매출 성장이 일어나는 에프터마켓으로 나뉜다. 에프터마켓을 모조품이라고 무시하기 쉬운데, 반도체 팹에 들어가는 어떤 소부장이라도 퀄 통과에 최소 2년이 걸리므로 모조품도 사실상 진짜베기(?)다.

통상적으로는 고부가가치 장비에 들어가는 부품 또한 고부가가치 제품이다. ex) EUV관련 부품

8) 장비 기업

반도체는 각 과학 분야에서 최고의 기술들을 접목시켜 진행하는 종합예술이다. 그러한 과정에서 여러가지 최첨단 기술이 적용되는데, 이러한 기술들이 반도체 팹에서 직접 개발되기도 하지만 몇몇 장비기업들이 고객사(팹)의 니즈를 먼저 파악해 개발하기도 한다. 기술 장벽이 워낙 높기 때문에 선점하면 최소3년 이상의 해자를 누릴 수 있으며, 그로 인한 GPM 또한 어마어마하다.

장비라는 물건 특성 상, 팹의 CAPEX에 매출이 좌지우지 될 수 밖에 없다는 단점이 있지만, 선단공정이 조급한 팹에게 '쓸 수 밖에 없는' 장비를 만드는 기업은 그러한 단점을 충분히 커버하고도 남는다. 장비기업을 투자할 때는 1) 반도체 상승 사이클의 시작(CAPEX)을 발라먹겠다(일회성) 2) 엣지 있는 장비를 가진 기업을 고르겠다(지속성) 두 가지 포지션이 있다고 볼 수 있다.

최근 미세화로 인해 난이도가 올라가면서 메인 공정 사이에서, 수율 향상에 조금이라도 도움 되는 디테일들이 주목 받고 있는데, 이러한 니즈를 빨리 파악한 장비 기업들은 본인들의 기술력으로 스펙트럼을 넓히고 있다. 예를 들어, 식각 공정의 A를 잘하는 기업이 증착 공정의 A도 잘할 수 있다는 것을 증명하기 시작한 것이다.

추가적으로 전공정이 후공정 대비 기술력이 높다고 평가받으며 CAPEX 사이클의 변동이 덜한, 비메모리 팹 향이 프리미엄을 받는다. 그리고 상승사이클에서 장비가 소부장 중에서 제일 빨리 올라타고, 하락사이클에서는 제일 빨리 얻어터진다.

9) 기판(PCB) 기업

기판 사업은 원래 사양사업으로 기술력 높은 공법이나 기판이 아닌 이상, PER 10을 넘기가 어려웠다. 하지만 어드밴스드 패키징(5.3항목)이 주목받고, 기판의 중요성이 대두되면서 국내 기판업체들에게 '미래'가 생겼다. 기판업계 자체가 재편되고, 각자 갈 길이 생기면서 경쟁이 완화된 것이다.

물론 기술력 높은 기판을 제조하기 위해서는 비싼 장비가 필요하므로 높은 CAPEX가 필요하다. 또한, 어드밴스드 패키징이라는 것이 반도체 팹에서 주도권을 잡고 하는 것이기 때문에, 반도체 제조 업체들과의 협업이 중요하다. 그러한 레퍼런스와 증설자금을 보유한 기판 업체들은 이번 어드밴스드 패키징의 흐름에 올라탈 수 있을 것이다.

그리고 여기서 빈틈이 있는데, 주요 플레이어들이 선단 기술에 집중하면 레거시 제품은 소외된다. 그런 흐름 속에서 올해 초 이수페타시스 같이 끝까지 살아남아서 상승사이클을 혼자 발라먹을 기업도 눈여겨 볼 필요가 있다.

10) OSAT

파운드리 및 IDM에서 반도체 물량을 공급받아 패키지 및 테스트를 진행하는 기업이다. 보통은 원가절감 및 인력효율화를 위해 하청에 가까운 기업이다. 비메모리 반도체는 다품종이기 때문에 이러한 구조가 효율적인데, 메모리 반도체는 소품종이기 때문에 이러한 구조가 비효율적이다. 그래서 비메모리 파운드리 및 팹리스가 많은 대만/미국의 OSAT는 업체들이 국내업체들 대비 압도적으로 크다.

국내 업체들도 비메모리 반도체 패키징 및 테스트 사업을 영위하지만, 아직까지 의미있는 물량을 받아내지 못하며 저부가가치 제품이 많다. 아직까지는 국내 대형 IDM업체들이 생태계 형성에 소극적인데 앞으로의 행보가 지켜볼 필요가 있다. 본 포스팅에서 후공정 및 어드밴스드 패키징을 이야기하면서 OSAT업체들을 지속적으로 언급할 예정이다.

11) 인프라 기업

CCSS, 클린룸, 진공펌프 같은 제품군을 다루며, 반도체 제조 팹 건설시 매출이 발생하는 기업이다. 매출이 지속적이지 않기 때문에 모멘텀 플레이가 강하며, 반도체 업사이클의 제일 선두에 있다.

1.5 반도체 기술 및 원리(HARD)

( 슬슬 어려워집니다....꼭 필요하지는 않지만, 반도체 종류별로 공정 상 차이를 이해하려면 보고 가는게 좋아유)

반도체가 전기/전자공학과 관련된 지식이 많다보니, 기술 이해에 대한 난이도가 매우 높다. 본 항목에서 간단히 정리하고자 하는데, 글쓴이는 전기공학을 포기한 공대생이라 부족함이 많다. 그래서 따로 서치해보심이 더 도움 될 듯 하다.

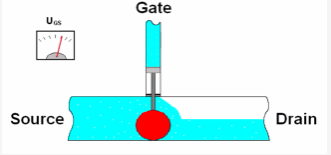

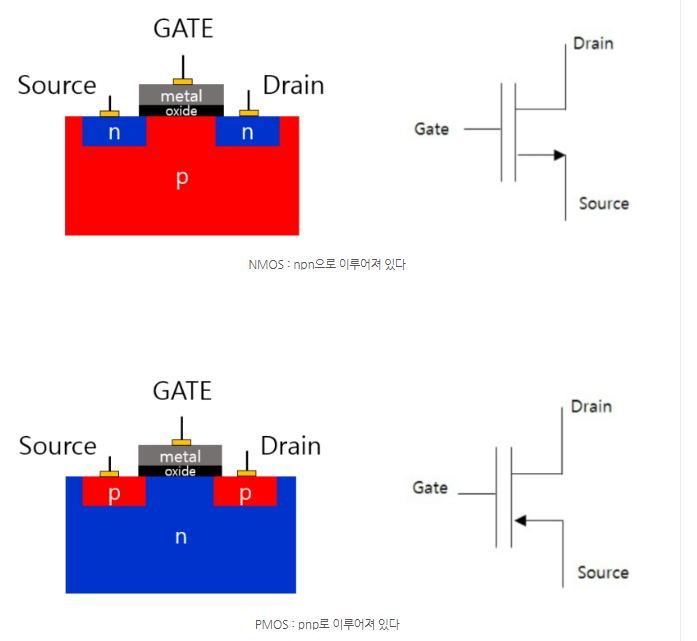

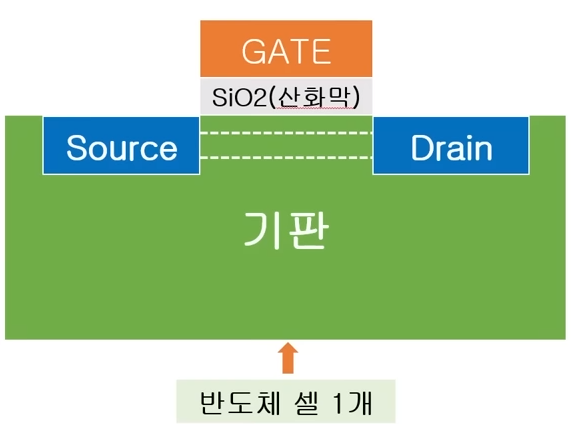

1) MOSFET

Metal Oxide 세미컨덕터 필드 이팩트 트랜지스터. 트랜지스터의 한 종류이다. 게이트에 Metal, 그 사이에 Oxdie, 기판에 Si이 쓰여 MOS라는 명칭이 붙었다. 게이트에 전압이 가해지면(문턱전압), 소스에서 드레인으로 전류가 흐른다. 트랜지스터의 주요 목적은 증폭 or 스위칭인데, MOSFET는 스위칭에 최적화된 트랜지스터다. 그래서 아날로그보다 디지털에 주로 쓰인다.

반도체 셀 하나에 들어가는 MOSFET

게이트: 전도성 소재로 전압이 가해지는 곳이다. 이곳에 어떠한 전압이 가해지냐에 따라 트랜지스터의 역할이 정해진다.

문턱전압: 게이트에 가해지는 전압의 임계점. 문턱전압을 넘겨야 채널이 형성되고 MOSFET를 동작하게 만든다.

소스: 채널을 형성하는 전자/정공을 제공한다.

드레인: 채널을 통해 이동해 온 정공/전자를 받아들인다.

캐리어: 채널을 통해 움직이는 정공 및 전자를 일컫는 말.

채널: 소스와 드레인 사이의 통로. 채널이 형성된다=정공이나 전자가 움직인다=전류가 흐른다.

산화막: 누설전류를 막아주는 절연막의 역할을 한다.

MOSFET의 동작원리를 간단히 보면 다음과 같다. 게이트에 문턱전압을 넣어주면 소스와 드레인을 막고있던 부분이 풀리고 소스에서 드레인으로 캐리어들이 이동하는 것이다.

MOSFET는 n형반도체와 p형반도체의 배열에 따라 다음과 같이 나뉜다.

NMOS: 전자가 이동하여 동작하는 트랜지스터. 소스와드레인이 n형, 기판이 p형. 문턱전압이 (+)일때 동작. 전자의 움직임이 정공보다 빠르므로 NMOS를 많이 쓴다.

PMOS: 정공이 이동하여 동작하는 트랜지스터. 소스와드레인이 p형, 기판이 n형. 문턱전압이 0V일때 동작.

CMOS: NMOS와 PMOS가 합쳐진 형태. 2개의 트랜지스터로 이루어짐. CMOS 한 개로 하나의 인버터를 만들 수 있어 활용도가 매우 높다. CPU, SRAM, CIS에 사용된다.

STI: CMOS에서 NMOS와 PMOS를 분할시켜주는 역할. 실리콘 산화막을 통해 절연역할을 한다.

2) MOSFET의 발전

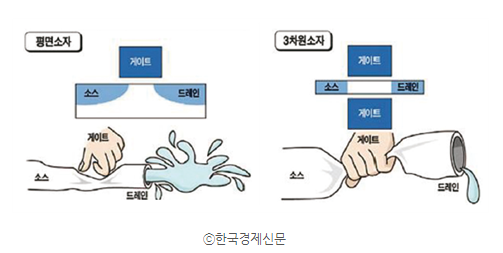

반도체가 미세화되면서 소스와 드레인의 거리가 줄어들고, 그로 인해 짧은 채널 효과가 발생한다. 해당 문제들을 해결하기 위해 MOSFET는 구조적으로 변화하고 있다.

Planar FET: 2차원 평면 구조의 MOSFET. 기존에 자주 쓰이던 트랜지스터 형태다.

FinFET: 3 Gate on channel. 채널을 3면에서 게이트가 감싸는 것이다. 게이트가 감싸서 컨트롤도 쉬워지고, 채널의 길이도 늘어난다. 삼성은 14nm, 인텔은 22nm, TSMC는 16nm부터 도입했다.

GAA(Gate-All-Around): 채널을 4면에서 게이트가 감싸는 동시에 적층구조로 올려 컨트롤을 더욱 더 늘린다. 삼전은 MBCFET라는 이름으로 3nm부터, TSMC는 나노시트 트랜지스터라는 이름으로 2nm부터 도입할 것으로 보고 있다.

>>>2차원에서 3차원으로 넘어가면서 노광+식각+증착 의 공정은 더 늘어난다.

※짧은채널효과: 채널이 짧아질수록 생기는 여러가지 문제를 말한다. 양자 터널링이 대표적인 문제다. 양자 터널링은 의도치 않게 소스의 전자 및 정공이 드레인으로 넘어가는 현상으로, 누설전류를 발생시킨다. FinFET 및 GAA를 도입할 경우 다음과 같이 개선됨을 볼 수 있다.

3) 실제 반도체 구조 및 동작원리

반도체는 무수히 많은 셀로 이루어져있고, 이 셀의 구조는 반도체 종류마다 다르다. 이 셀의 갯수가 반도체의 용량이며, 그러한 셀들을 통제/관리하는 것이 Periphery(주변회로)이다. 비메모리 디지털 반도체는 대부분 CMOS를 이용하므로 위에 설명된 CMOS를 참고하고, 본 항목에서는 범용화된 제품인 D램과 낸드플래시에 대해서만 파악해 보자. 비메모리 구조에 대해 더 자세히 알고자 하면 다음 포스팅을 참고하시길 바란다.

(참고로, 셀 구조에 나오는 기판은 반도체의 베이스인 Si웨이퍼를 의미하는 것이다)

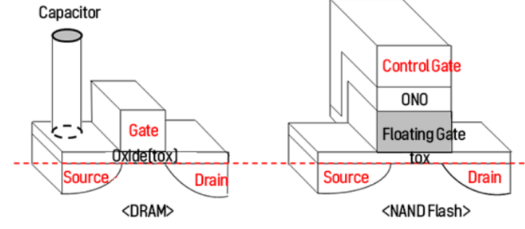

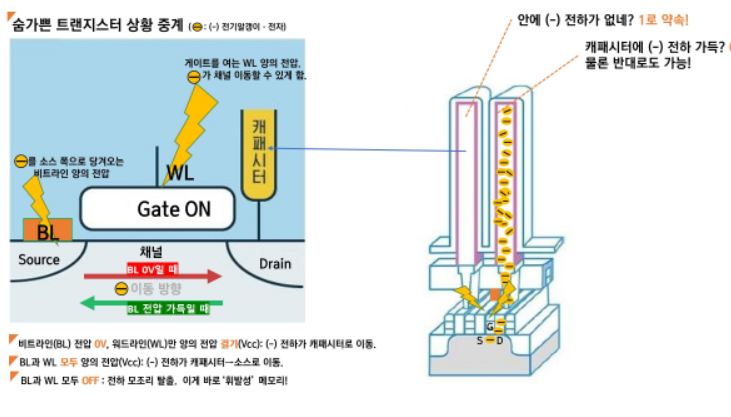

D램

구조: NMOS 트랜지스터 위에 캐패시터가 1개 있는 구조. 캐피시터에 데이터를 저장한다. 다음 글을 꼭 읽으시길 권한다.

출처-삼성전자

동작원리: 다음 사진 하나로 완벽히 설명이 된다. 게이트가 문지기를 하고 문지기에 전압을 걸어서 열고, 비트라인을 통해 데이터를 저장/삭제 하는 것이다.

NAND

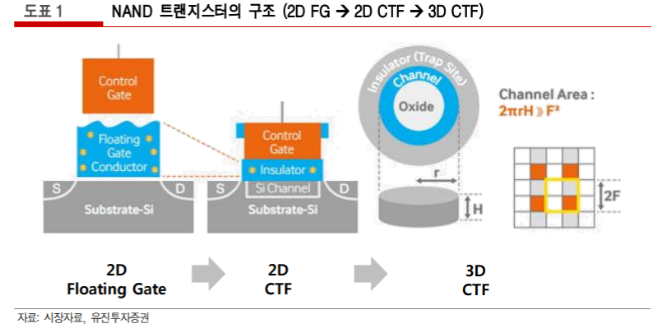

구조: 낸드는 1970년대부터 시작하여 다음과 같은 변화 과정을 지났다.

2D플로팅게이트: nMOS에 플로팅게이트를 합친 구조이다. 그렇다 보니 게이트가 CONTROL게이트와 플로팅게이트로 총 2개이며, 그 사이에 절연막이 있어 2개의 캐패시터같은 느낌을 준다. 플로팅게이트(Nitride)에 데이터를 저장하는 방식이다.

2D CTF: 플로팅게이트 없이 컨트롤게이트만으로 된 구조다. 게이트 높이가 낮아져서 미세화에 용이하다. 이 컨트롤게이트를 전하트랩형 게이트라고 부른다.

3D CTF: 2D CTF를 3D 원통형 구조인 GAA로 변환한 것이다. 컨트롤게이트가 원형이라서 접촉면적이 넓다.

3D VNAND: 오늘날 주력이 된 낸드플래시.높은단에서 낮은단으로 구멍을 뚫어 층마다 전극을 연결. -삼성전자의 비유로는 “200미터 높이의 건물 옥상부터 바닥까지 5미터 지름으로 수십억 개의 구멍을 한 번에 뚫고, 각 층에 2개의 문으로 전자를 이동시킬 수 있는 양문 엘리베이터를 설치하 기술" 이라고 한다.

동작원리: 게이트에 전압을 가하면, 플로팅 게이트 or 전하 트랩형 게이트에 채널의 전하가 축적된다. 이것이 1을 나타나게 되고, 반대로 기판에 전압을 가하면 전하가 빠져나와서 0을 나타나게 된다.

4) 공정의 미세화 및 고단화

기업별로 몇 나노 공정이니 하는 이야기들은 대부분 트랜지스터의 게이트 길이를 의미한다. 게이트 길이를 줄일수록 같은 크기의 웨이퍼에 많은 트랜지스터를 넣을 수 있기 때문에 공정 단위는 중요할 수 밖에 없다. 하지만 FinFET구조가 나오면서 회로 단위에 큰 의문이 생겼다.

FinFET이나 GAA에서 게이트는 3차원 구조로 변하고, '채널길이=트랜지스터길이=게이트길이'가 성립할 수 없기 때문이다. 그래서 이제는 공정의 단위가 절대적인 스펙이 될 수 없다는 의견이 많다. 실제로 반도체 팹 기업에서는 타기업 대비 더 낮은 공정단위를 뽐내며 마케팅 용도로 쓰이고 있다. 실제로 TSMC의 N4는 4nm가 아닌 5nm의 플러스 버전이라는 이야기가 있고, 파운드리 기업별로 같은 나노단위라고 해도 트랜지스터 집약도가 많이 다르다고 한다.

즉, 최선단 업체들간의 몇 나노 공정이라고 이야기하는 것들은 각 기업에서 본인들의 '前공정단위 대비하여' 를 나타내는 표현이라고 보면 된다 (자기만의 싸움). 오히려 성능을 따질 때는, 단위 면적당 트랜지스터의 갯수 및 다음 트랜지스터 구조(GAA)를 얼마나 빨리 안착시키냐가 더 중요하다고 한다.

그리고 반도체 종류별로 구조가 다르기 때문에, 종류별로 미세공정을 논하는 것이 맞다. 로직반도체들이 주류인 파운드리 시장은 싱글나노에 들어간 반면, D램은 캐피서터의 종횡비 문제로 10나노대에 머물러 있고, 낸드는 적층으로 효율을 뽑아낼 수 있게 되면서 미세화보다 고단화가 중요함을 볼 수 있다.

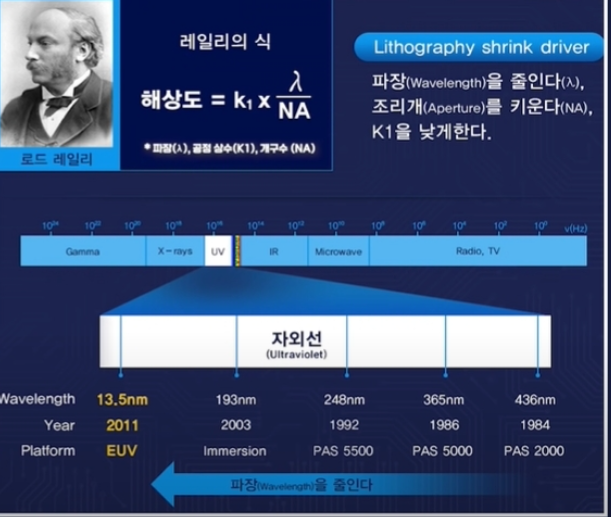

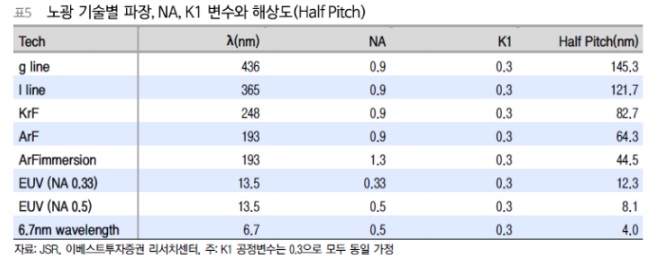

5) 노광에 대한 여러가지

전공정(2.1) 항목에서 다룰 노광에 대한 deep한 이야기들이다. 반도체 집적도 및 미세화와 직접적으로 관련된 공정으로, 다뤄야할 이야기가 많다.

레일리의 식

반도체 미세공정의 핵심은 노광은 미세화와 직결된다. 노광의 미세화는 여러가지 요인들에 결정되는데, 레일리의 식이 그것을 보여준다.

CD: 인쇄가능한 최소 선폭=해상도.

람다: 광원의 파장

NA: 개구수. 렌즈가 모을 수 있는 정보의 크기 = 렌즈의 크기. 굴절률이 클수록 그 크기가 크다.

k1: 반도체 제조 공정과 관련된 상수.

노광기를 만드는 장비업체는 CD값을 작게하는 것이 기술력이라고 볼 수 있다. 선폭이 작다는 것이 미세화를 의미하기 때문이다. 그러기 위해서 레일리의 식을 참고하면, NA를 키우는게 핵심이다.

광원 종류와 파장

KrF: 248nm, 크립톤과 불소의 조합으로 레이저 사용. 80nm까지 패터닝 가능하다.

ArF: 193nm, 아르곤과 플루오라이드 조합으로 레이저 사용. 38nm까지 패터닝 가능하다.

F2: 157nm,

EUV: 13.5nm,

X-RAY: 1nm이하

(DUV= Deep Ultra Violet, 보통 KrF와 ArF를 말함)

광원의 파장은 정해져있지만, 공정의 발전으로 파장보다 더 미세화된 회로를 새길 수 있으므로 파장의 단위가 회로의 단위와 완전히 일치하지는 않다. 비슷한 정도.

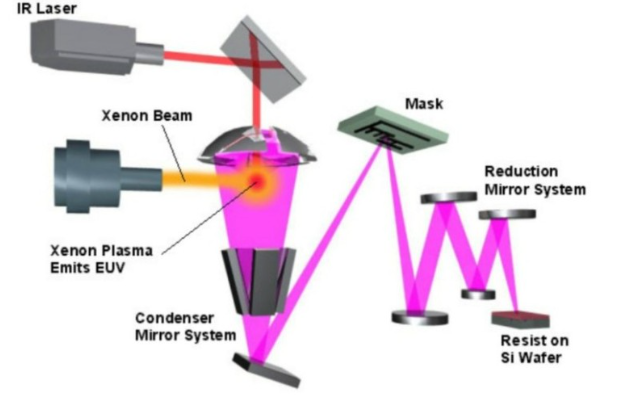

EUV에 대해

액화주석을 1초에 5만번 떨어뜨려 CO2 레이저로 입사시켜 플라즈마를 형성한다.

흡수가 잘되서 고진공 작업환경이 필요하다.

DUV대비 에너지가 높아서 굴절이 심하다. 그래서 투과형 렌즈를 쓰지 못하고 반사형 렌즈(거울)를 이용해야 한다.

대부분의 노광 부품들을 EUV전용으로 만들어야한다.-PR/마스크/펠리클/렌즈(반사형)

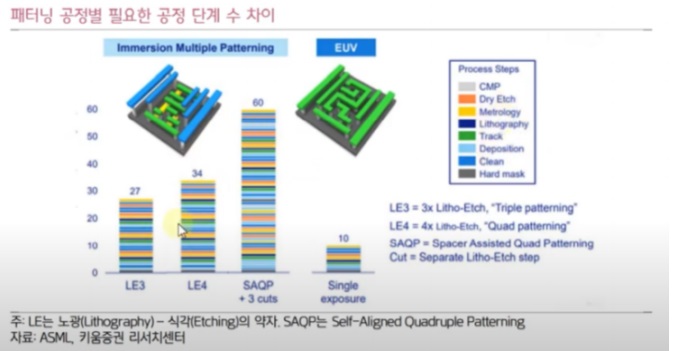

'공정 스텝 수 감소 > TAT 감소 > 비용절감' 효과를 볼 수 있다.

멀티패터닝의 단점

EUV를 사용하면 균일도, 정확도가 상승한다.

NA에 대해

NA는 빛의 굴절률을 의미한다. NA가 높아질수록 빛의 굴절률이 적어지고 해상력은 증가한다. NA를 증가시키려는 노력으로는 다음과 같다.

렌즈 크기를 키운다 > 장비 공간도 커져 문제가 있다.

마스크 크기를 키운다 > 팹 내의 마스크 관련 장비들도 다 바꿔야 한다.

마스크 제작 단계에서 미리 배율을 조정한다. 생산성도 유지되고 NA도 증가한다.

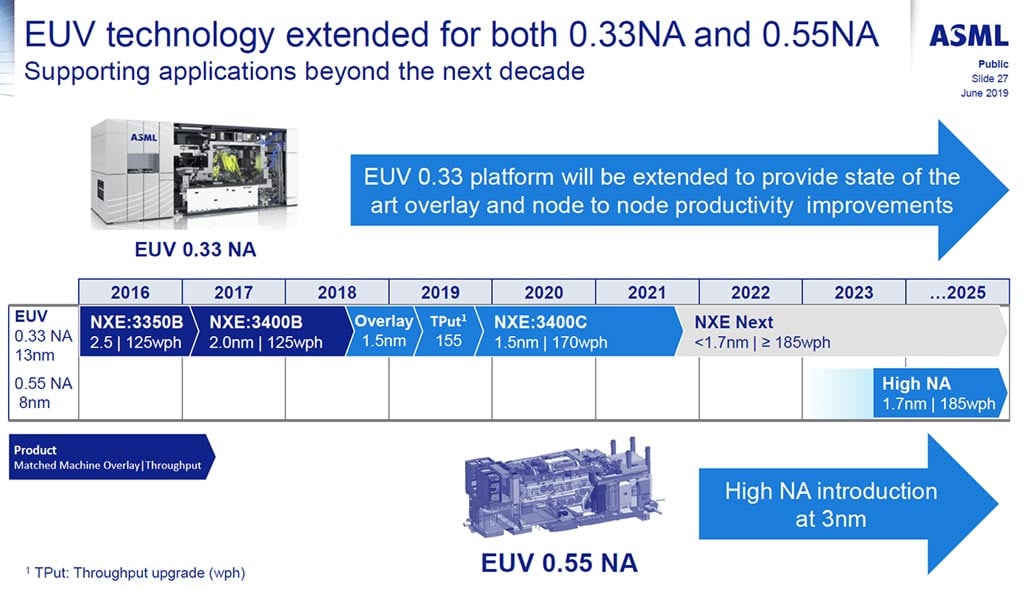

현재 ASML에서 개발한 EUV 노광기는 0.33NA와 0.55NA 시리즈가 있다. ASML에서는 NA도 올리는 동시에 광원의 파워도 올리려고 하는데, 이렇게 되면 소재 부품단에서도 발전해야한다. EUV 소재부품 만들기도 어려운데, High-NA버전을 추가로 개발해야한다.

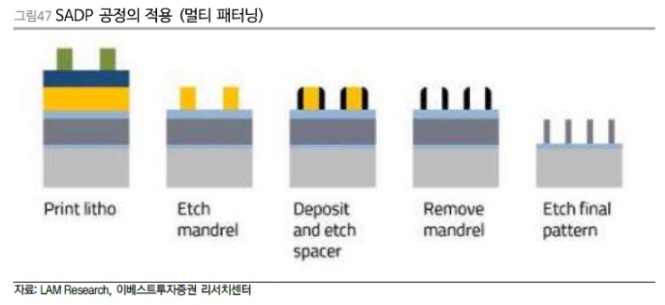

멀티패터닝: 단일패터닝+DUV 로는 미세화가 어렵기 때문에 패터닝을 여러번 하는 방법. 멀티패터닝이 기존 광원으로 미세화를 할 수 있다는 점은 장점이나, 다른 공정들도 추가로 늘어나면서 생기는 비용을 무시하지 못한다. 광원을 업그레이드 할 것인가, 패터닝을 늘릴 것인가는 계산기를 두드려봐야 안다(EUV는 보통 7나노에서 하면 이득이라고 함).

LLE방식: 리소 > 리소 > 에칭. 정렬도가 좋지 않음.

LELE방식: 리소 > 에칭 > 리소 > 에칭. PR의 종횡비 문제로 하드마스크 사용.

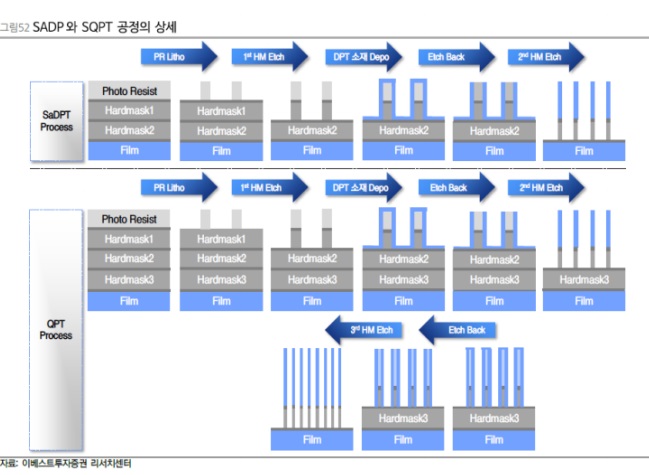

SADP방식: 자가정렬 스페이서 더블 패터닝 기법. SADP 사용시 ArF 광원으로 20nm까지 가능하다.

SAQP방식: 자가정렬 스페이서 쿼드러플 패터닝 기법. SADP를 두번 반복. SAQP 사용시 ArF 광원으로 10nm까지 가능하다.

하드마스크: 멀티패터닝을 하면 PR의 종횡비 문제로 무너질 수가 있다. 그래서 하드마스크를 사용한다. 하드마스크에 노광을 해서 에칭하고 남은 하드마스크가 PR의 역할을 해주는 것.

기존에는 ACL(비정질탄소막)을 CVD로 증착하고 위에 SiON을 CVD나 SOH로 증착.

속도가 느리고 비용이 많이 들어 ACL 증착에 SOH 방식 도입.

SOH: 스핀 온 하드마스크. 스핀코팅방식으로 증착하는 것.

1.6 반도체의 갖가지

1) 반도체의 대표적인 트레이드오프: 성능이 좋아지면 발열과 전력소모가 심하다. 그걸 잡는게 반도체 업체들의 기술력이다.

2) 폰노이만 구조: 대부분의 PC에 쓰이는 컴퓨팅 시스템 구조. '중앙처리장치-메모리-프로그램' 와 같은 형태. 중앙처리장치가 메모리의 데이터를 읽고 쓰는 것으로 병목현상이 생길 수 밖에 없다.

3) 뉴로모픽 컴퓨팅: 인간의 뇌와 같은 구조를 모방한 인공신경망 형태의 집적회로이다. 연산과 저장을 서로 다른 칩을 이용하는 폰노이만 구조와 다르게, 두개를 하나의 유닛으로 통합하는 구조이다. 로직반도체보다 높은 성능의 뉴로모픽 칩을 만드는 것은 어렵기 때문에, 로직반도체와 메모리반도체 사이에서 보조역할을 하는 칩으로 자리잡고 있다.

4) 전압이 낮을수록 전력이 낮다고 보면 된다.

5) 반도체 제조 과정은 진공에서 이뤄져야 하므로 중간에 팹이 중단되면 웨이퍼를 폐기처분해야한다.

6) 반도체 팹 전쟁에서 기술력도 기술력이지만, 자본의 역할이 크다. 삼전은 매년 장비값으로만 10조원 넘게 현금지출이 발생한다.

7) 그 말은 고정비 지출이 매우 크다는 것을 의미하고, 제품 가격이 하락해도 쉽게 장비를 놀릴 수가 없다(공급이 유연하지 못하다). 반대로, 영업레버리지가 터지기 쉬운 구조다.

2. 반도체 공정

어느 기술섹터나 그렇지만, 공정/기술에 대한 깊이는 무작정 공부하고자 하면 한도 끝도 없다. 그래서 접근 방식을 설정하고 들어가는게 중요한데, 반도체를 포함한 기술섹터를 접근하는 방식은 크게 2가지가 있다고 생각한다. 1) 기술에 대한 깊이를 가져가 강력한 엣지가 있는 기술을 파악한다. 2) 기술의 너비를 가져가 선단업체 및 팹업체들의 낙수효과를 가져갈 기업을 빠르게 파악한다.

본 포스팅의 글쓴이가 지식에 대한 깊이 및 이해력이 없는 것도 있지만, 국내 반도체 소부장의 스펙트럼이 워낙 넓기 때문에 너비만으로도 충분히 좋은 반도체 투자를 할 수 있다 생각한다. 그래서 본 포스팅에서는 너비를 중점으로 학습하고자 한다. 깊이에 대해서는 심화편으로 정리하거나 개별 기업으로 정리할 예정이다.

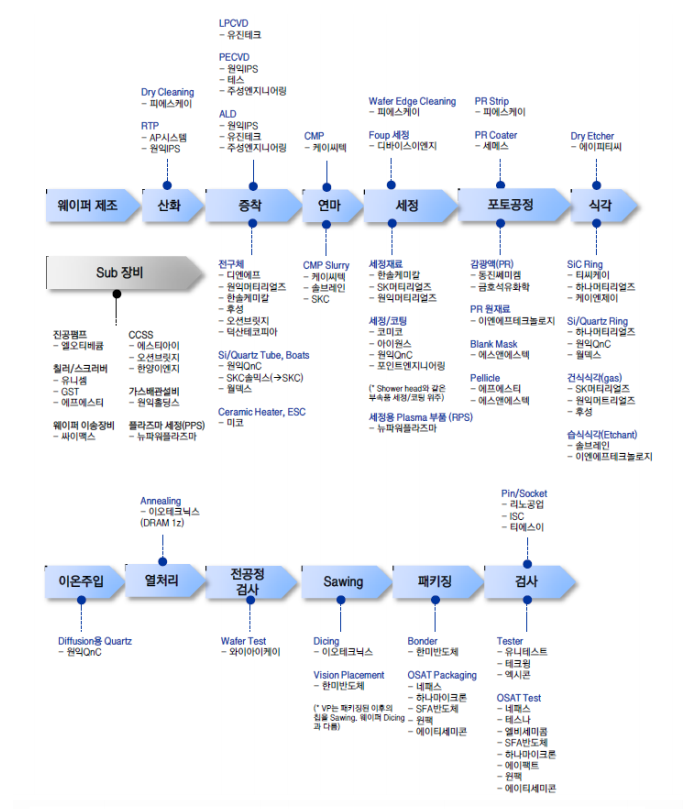

반도체는 정말 수 많은 공정을 거쳐 탄생하게 되는데, 그 기술의 난이도가 굉장히 높고 복잡하기 때문에 큼직큼직하게 전공정/후공정으로 나누고, 핵심이 되는 공정은 다시 8대공정으로 정리해 부른다. 8대 공정이라고 8번의 공정만 지나면 끝나는 게 아니라, 만들고자 하는 칩에 따라 특정 공정을 더 넣거나 빼기도 하며 어떤 구간을 반복하기도 한다. 웨이퍼라는 물질에 원하는 설계를 매우 작게 표현하기 위해 그림 그리고 깍고 붙였다가 다시 깍았다가 난리부르스 인 것이다. 핵심 8대 공정 이외에 자주 쓰이는 공정들은 기타공정으로 빼서 정리하였지만, 8대 공정이라는 키워드에 얽매여서 반도체 제조를 바라보지 않기를 추천드린다.

8대공정

웨이퍼-산화-포토-식각-박막-금속배선-테스트-패키징

2.1 전공정

반도체 공정은 기술집약적이면서 기술개발이 끊임없이 일어난다. 그래서 레거시 제품과 선단 제품이 계속해서 구분된다. 이러한 흐름 속에서 레거시 공정이 무시받기 십상인데, 반도체가 아무리 미세화되더라도 하나의 칩에서 수 많은 층과 공정반복이 이루어지기 때문에 여전히 레거시 공정이 필요한 경우가 많다. 즉, 1000원짜리 칩을 만드는데 굳이 ALD를 쓸 일도 없는것이고, 최선단 CPU의 '금속배선'에 EUV를 쓰는 것이 비용 낭비라는 것이다.

1) 웨이퍼

웨이퍼 제조에 대한 공정은 반도체 팹에서 진행하는 것이 아니다. 반도체 팹은 그저 만들어진 웨이퍼를 들고 오는 것이다. 또한 Si웨이퍼에 대해서는 서열정리(5개업체)가 되었기 때문에, 웨이퍼에 대한 디테일은 생략했다. 물론 화합물 웨이퍼는 다른 이야기다(5.4 항목에 정리).

1-1) 잉곳 제작

1-2) 웨이퍼 제작: 다이아몬드 톱로 잉곳을 얇게 절단.

1-3) 웨이퍼 연마(CMP공정): 절단된 웨이퍼는 표면이 거칠어서 연마가 필요하다. 패드에 압착시킨 후 슬러리(연마제)를 흘러주면서 고속으로 회전시킨다. CMP는 화학적 처리를 통해 기계적 연마가 쉽게 되도록 한 뒤에 기계적 연마를 하는 하이브리드 공정이다. 공정 초기 웨이퍼 표면 연마에도 쓰이지만, 다음과 같은 경우에도 필요하다.

금속배선 시 W(텅스텐)를 산화시킨 뒤 CMP

금속배선 시 다마신공법

패키징 직전 CMP

CMP장비는 연마장치, 세정장치, 슬러리공급장치, 폐액처리장치, 공정 모니터로 구성되며 무엇을 연마하느냐에 따라 CMP종류와 슬러리가 달라진다.

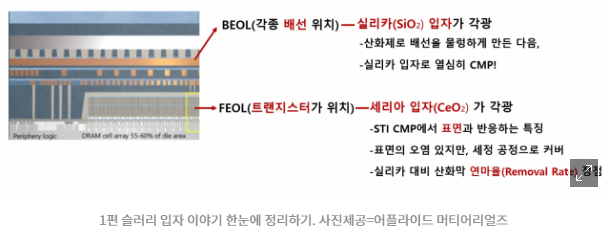

버핑CMP: 산화물 CMP 후에 생긴 이물질을 제거하는 CMP이다. 산화물 CMP 빈도가 증가하면 따라서 증가한다.

산화물CMP: STI공정 중 생기는 옥사이드를 CMP한다. 범용으로 실리카 슬러리를 이용하고 세리아 슬러리의 비중이 증가하는 추세다.

금속CMP: 금속배선과 패키징 전 CMP에 주로 쓰인다. 기술력이 가장 높으며, 실리카 슬러리를 사용한다.

2) 산화

나중에 만들어질 회로를 위해 또는 만들어진 회로에 누설전류 차단을 목적으로 진행하는 공정이다. 웨이퍼에 고온의 산소를 뿌려 SiO2를 만든다. 이렇게 만들어진 산화막은 이온주입 공정에서 확산방지막으로(디퓨전마스크), 식각공정에서는 잘못 식각하는 것을 방지, 게이트와 기판 사이에 쌓아 누설 전류를 차단하는데 쓰인다(게이트 옥사이드). 즉, 절연/보호의 목적으로 공정 중간중간에 계속해서 쓰인다.

산화막을 형성하는 방법은 크게 '성장'과 '증착'이 있는데, 열산화방식이 대표적인 성장 방법인 것이고, 우리가 흔히 말하는 산화 공정이 이 방식을 의미한다. 증착공정으로 산화막을 형성하는 것은 5) 증착 항목에서 다뤘다.

열산화방식: 열을 이용해 산화막 형성. 참고로, 산화막을 형성하기 전에 웨이퍼 위에 방해가 되는 자연물들을 제거하는 웨이퍼 클리닝 작업(드라이 클리닝)을 한다. 열산화 방식은 가스가 나가고 들어오는 부분이 상대적으로 불균일하므로 앞뒤로 더미웨이퍼를 배치한다.

건식산화: 산화막 성장 속도가 느리나, 얇고 전기적 특성이 좋은 고품질 산화막 생성시 사용. 주로 게이트옥사이드 형성에 사용된다.

습식산화: 수증기를 섞어서 속도가 빠르나, 밀도가 낮고 두꺼워서(건식 대비 5~10배), 주 중요도가 떨어지는 마스킹/보호막 층으로 이용한다.

※열산화 장비

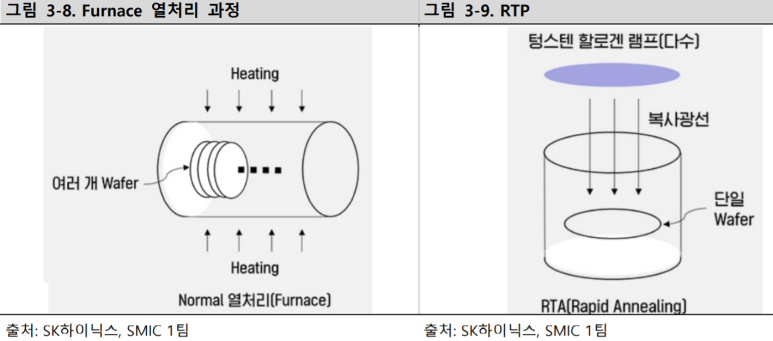

Furnace TYPE: 고온으로 올리는데 시간이 걸리고 컨트롤이 어려워, RTP가 대세다.

RTP: 급속도로 가열하고 열처리를 정밀하게 제어한다.

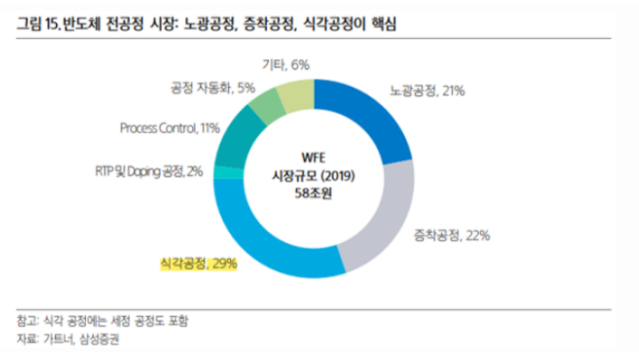

3) 포토(패터닝, 리소그래피)

반도체 총 공정 비용의 30%이상을 차지하는, 반도체 공정의 꽃이다. 빛을 이용하여 웨이퍼에 패턴을 새기는 공정이다. 패턴을 새긴다는 것이 어떤 공정을 위한 밑바탕을 그리는 것인데, 그러한 공정이 대부분 식각이나 이온주입에 해당한다. 그렇기 때문에 포토 공정은 자주 쓰일 수 밖에 없고, 거기에다 소부장이 고가이기 때문에 비용이 큰 공정인 것이다.

3-1) 웨이퍼 수분 제거: 웨이퍼 표면에 HMDS라는 물질을 도포하여 수분제거.

3-2) 감광액(PR) 도포

감광액: 빛을 통해 광화학 반응을 일으키는 물질. 광원에 따라 쓰는 감광액이 다르다. solvent/resis(polymer)/pac로 이루어져 있으며, resin이 핵심 재료다.

positive PR: 광원에 노출된 영역이 녹아내리는 것.

negative PR: 광원에 노출되지 않은 영역이 녹아내리는 것.

스핀코팅: 웨이퍼가 안착된 판을 회전시켜 균일하게 PR이 도포되도록 하는 방식.

3-3) 소프트 베이크: 열을 가해 PR의 solvant를 증발시키는 과정. 마이크로웨이브 히터나 IR히터를 사용.

3-4) 노광: 광원을 쏘아 패터닝을 만드는 과정. 반도체 공정의 핵심. 어느 패턴을 새길 것인가는 패턴이 이미 그려진 마스크로 결정되며, 빛은 마스크와 렌즈를 지나서 웨이퍼에 도달한다.

광원이 포토마스크를 지나는 과정에서 포토마스크에 오염물질이 있으면 마스크에 손상이 갈뿐더러, 패터닝에 문제가 생긴다. 그래서 펠리클이라는 마스크 덮개를 쓰는데, 계산기를 두드려서 쓸때도 있고 쓰지 않을때도 있다.

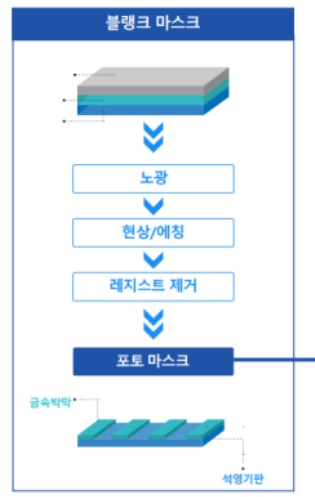

포토마스크(=레티클): 반도체 회로 설계도를 순도 높은 쿼츠(석영)에 새긴 것.

블랭크마스크: 회로 설계도가 그려지기 전의 마스크로, 쿼츠에 감광액을 뿌린 상태. 포토마스크 이전의 상태.

펠리클: 몸값이 비싼 마스크의 오염을 막기위한 일종의 마스크덮개. 광원에 따라 종류가 다르며, DUV용은 마이크로미터 단위인 반면, EUV는 나노미터 단위로 매우 높은 기술력이 요구된다.

렌즈: 포토마스크는 반도체에 새길 회로보다 크게 제작되므로, 노광을 할때 빛을 모아주는 역할을 한다.

3-5) 노광 후 베이크: 노광 후 가열 및 건조

3-6) 현상: DEVELOPER라는 현상액으로 회로 패턴이 새겨진 부분 이외의 PR을 제거하는 공정. 현재 puddle방식을 쓰고 있다.

3-7) 하드베이크: 한번 더 건조.

3-8) CD 및 패터닝 검사

4) 식각(에칭)

반도체 패턴이 새겨진 부분 이외의 산화막을 제거하는 공정으로, 전체 장비 CAPEX에서 30~40% 정도를 차지하는 중요한 공정이다. 식각의 종류는 다음과 같으며, 보통 건식식각 장비 및 기술이 습식식각에 비해 기술력이 높은 것으로 알려져 있다.

4-1) 식각 방식의 종류

습식식각: 화학용액 사용. 빠르지만 정확성이 떨어진다. 등방성의 문제 있다.

dip(immersion)방식: 식각 용액에 담궜다 빼는 방식.

spray방식: 스핀을 하며 스프레이로 뿌려주는 방식.

건식식각: 플라즈마를 이용. 정확성이 비교적 높아 밀도가 높아야하는 부분(D램의 캐패시터 같은)에 쓰인다.

화학적식각: CF4(할로겐)을 사용하여 Diffusion(확산)을 이용한다. 등방성의 문제 있다.

물리적식각: Ar(아르곤)가스를 이용하여 플라즈마에서 발생된 이온으로 뜯어내는(sputter) 방식. 이방성으로 정교하지만, 느리다.

화학&물리적식각(RIE): 이방성이면서 빠르다. 하지만 기술력이 높고 독한 가스가 많이 쓰인다. 선단 공정에 많이 쓰인다. TSV도 RIE를 통해서 진행된다.

ALE: 원자 단위 식각. 아직까지 개발 중이나, 반도체 미세화에 따라 수요가 늘어날 것으로 보고 있다.

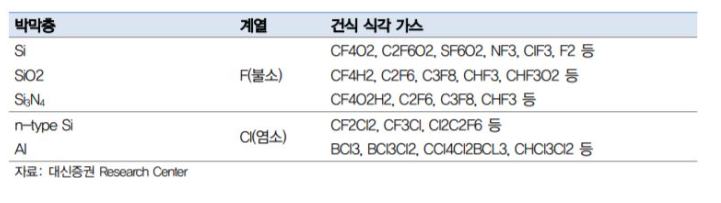

4-2) 무엇을 식각하느냐

식각공정은 무엇을 식각하느냐에 따라 그 장비와 방식이 달라진다.

유전체 식각(CCP방식)

컨텍홀 패턴 형성을 위한 식각이 대다수고, 산화막/질화막과 같이 절연체 역할을 하는 유전체를 주로 식각한다. D램의 캐패시터 종횡비 증가와 낸드플래시의 고단화로 유전체 식각 빈도가 높아지고 있다.

산화막에칭(게이트 및 컨텍홀 형성): F 및 Xe(제논)를 많이 사용한다.

질화막에칭(STI, Spacer공정): F를 많이 사용한다.

전도체 식각(ICP방식)

폴리실리콘이나 메탈을 식각하며, 유전체 식각 환경보다 덜 가혹하다.

실리콘에칭(게이트형성, STI공정): F > Cl > Br 순으로 많이 사용.

메탈에칭(게이트형성, 배선공정): Cl을 많이 사용한다.

4-3) 식각액/가스 및 부품

식각액/가스는 식각공정에 쓰이는 액체 및 가스로 무슨 식각이냐에 따라 그 종류가 달라진다. 크게 습식식각과 건식식각에 따라 달라지는데,

습식식각: 습식이기 때문에 식각'액'을 쓰고, 다시 불산계와 인산계, 초산계(아세트산)로 나뉜다.

불산계: 실리콘옥사이드 식각 및 세정용으로 많이 쓰인다.

인산계 : NAND 질화물식각에 주로 쓰인다.

초산계: 차세대 MOSFET인 GAA에 쓰인다.

건식식각: 가스를 이용해서 식각한다.

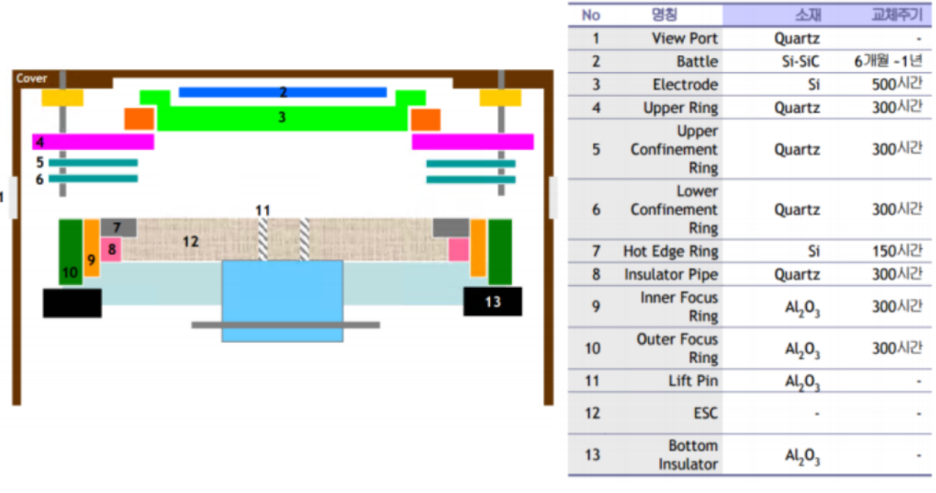

4-4) 식각 공정 소모성 부품

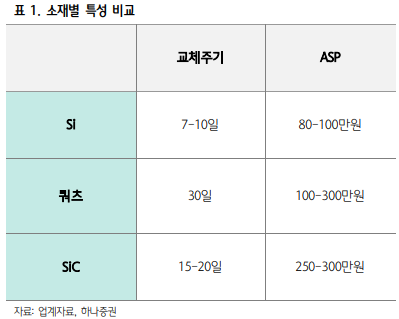

식각 공정에는 많은 부품이 필요하고, 무엇을 식각하느냐/무슨 부품이냐에 따라 적합한 소재가 달라진다. 소재는 크게 Si/쿼츠/SiC가 쓰인다.

Si: 실리콘.

SiC: 실리콘카바이드. 플라즈마 식각의 빈도가 높아질수록 SiC 수요는 높아질 수 밖에 없다. SiC는 포커스링 이외에도 ALD, 에피택시, Susceptor, 더미웨이퍼, ESC, HEATER 공정에도 사용되지만, 일본기업이 독점중이다. 또한 SiC의 원재료인 그라피트도 일본기업이 독과점중이다.

쿼츠: 식각공정보다는 확산(이온주입)공정의 TUBE와 BOAT에 주로 쓰인다. 쿼츠의 원재료는 미국/일본/독일기업들이 독과점중이다.

ELECTRODE(샤워헤드, 캐쏘드): 플라즈마 가스를 분사하는 부품. SiC를 사용하기도 하지만, Si가 주류이다.

포커스링: 웨이퍼 주변에 장착되어 웨이퍼 및 전극을 보호하고 웨이퍼 Edge까지 균일하게 식각하도록 도와주는 역할을 한다. Si/SiC를 골고루 사용하며, 낸드는 고단화가 진행되면서 식각난이도가 올라가고 SiC가 주로 쓰인다(96단 이상은 거의 SiC).

가이드링(아우터링): 상부에 위치하여 ELECTRODE를 고정시켜주는 역할을 한다. 쿼츠 및 알루미나가 주류이다.

ESC: 웨이퍼를 수평으로 고정시켜주는 부품. 물리적이 아닌 정전기의 힘만으로 탈착하며 대부분이 해외 수입이다.

이 부품들은 장비사에 납품하는 비포마켓과 반도체 팹에 납품하는 에프터마켓으로 나뉘는데, 자세한 이야기는 2편(기업)에 정리하였다.

5) 증착(박막)

웨이퍼에 뭔가를 씌우는 공정이다. 절연막/방지막/하드마스크를 위해 산화막/질화막을 씌울 수도 있고, 게이트나 배선형성을 위해 폴리실리콘 및 메탈물질을 씌울 수도 있다.

5-1) 증착 공정 주요 포인트

스텝커버리지(단차피복): 기판위의 두께와 벽면의 두께 차이가 없어야 좋다=스텝커버리지가 1에 가깝다.

균일도: 말 그대로 모든 면에 균일한 두께로 증착되었는가.

갶필: 내부에 구멍이 생기면 나쁘다.

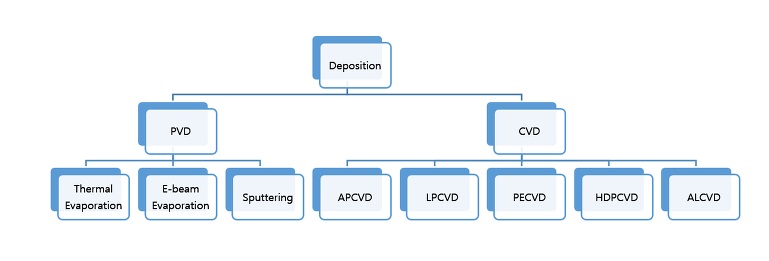

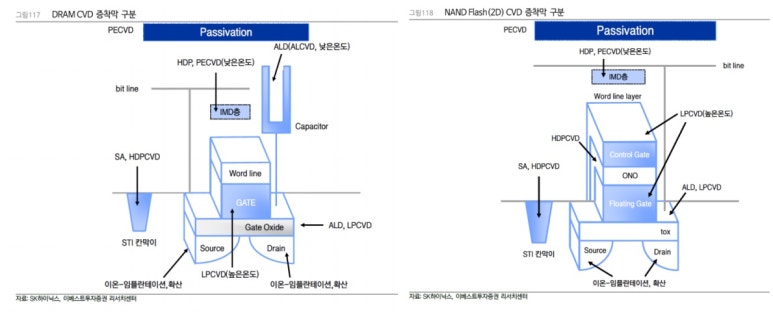

5-2) 증착 방식의 종류

증착은 대부분 진공에서 이뤄지며, 증착의 종류들은 다음과 같다.

PVD(물리적 기상 증착법): 금속 박막의 증착에 사용. 저온증착.

스퍼터링 방식: 아르곤 플라즈마를 사용하여 증착. 속도가 느리고 가스가 많이 필요하다. 또한 데미지 발생이 있어 열처리 공정을 추가로 해야한다.

증발(evaporation): 두껍게 필요한 부분에 적합해서 주로 금속배선 공정에서 메탈 증착에 많이 사용된다.

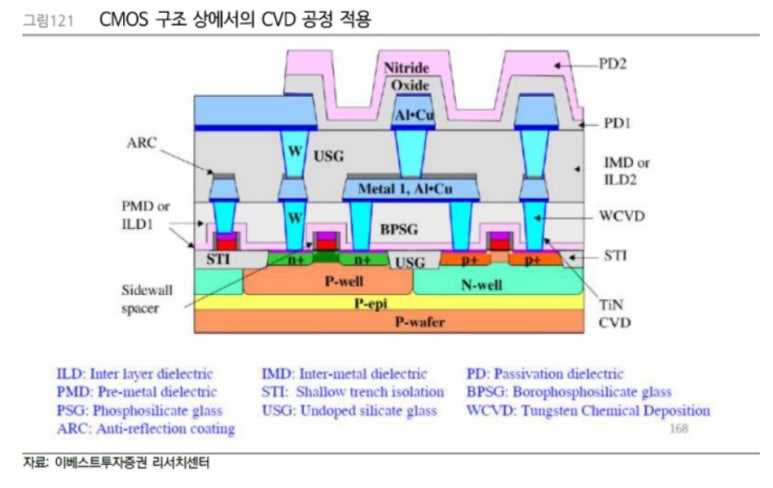

CVD(화학적 기상 증착법): 전구체 가스가 챔버에 유입되면서 증착. 고온증착.

APCVD: 상압CVD. 저렴하고 간단하며 빠르다. 균일도와 스텝커버리지가 나쁘다. 산화막 증착에 쓰인다.

LPCVD: 저압CVD. 고온공정으로 고품질 필름이지만 속도가 느리다. SiO2, Si3N4, Poly-Si 증착에 쓰인다.

PECVD: 플라즈마CVD. 저온공정으로 속도는 빠르지만 저품질 필름이다. IMD, Passivation 증착에 쓰인다.

HDPCVD: 고밀도 플라즈마CVD. 저온공정으로 스퍼터링을 이용해 고품질 산화막이지만 데미지가 크다. STI, IMD 증착에 쓰이며, PECVD를 대체해가는 추세다.

※STI: 트랜지스터 간의 분리를 위해 쌓는 절연막(산화막). SiO2와 Si3N4를 LPCVD로 증착하고 노광 > 식각 진행 > 어닐링 > SiO2를 HDPCVD로 증착 > CMP로 평탄화.

진공도가 높아지면 더욱 정밀하고 균일한 막을 형성할 수 있다. 대신 시간이 길어진다.

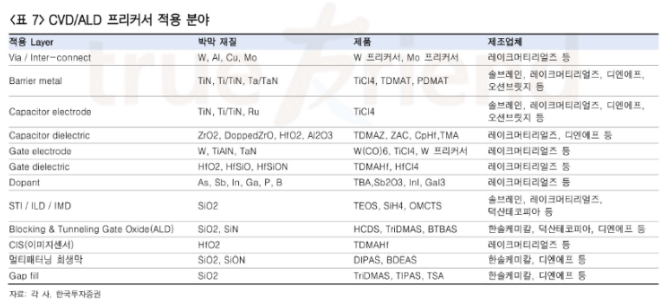

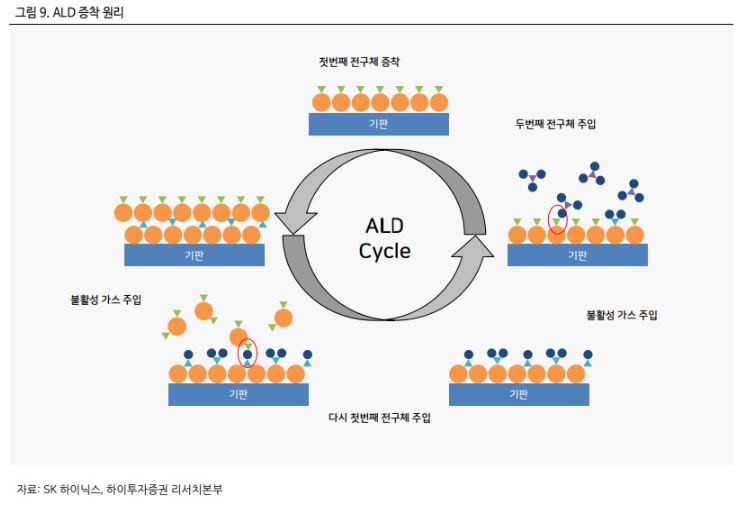

ALD(원자층 증착법): 매우 얇은 원자층 막을 겹겹히 쌓는 기술. 고품질필름에 nm단위 조절이 가능하지만 생산량이 낮다. 전구체를 투입 후 다른 가스를 유입시켜 반응시킴. D램의 캐피서터 유전막, Highj-k 게이트 유전막, 낸드의 아랫단 전극인 텅스텐 증착 및 터널 산화막/블로킹 산화막, interconnect, 멀티패터닝의 스페이서 증착에 쓰인다.

PEALD: 플라즈마ALD. ALD에서 플라즈마를 일으켜 속도를 향상시키는 증착.

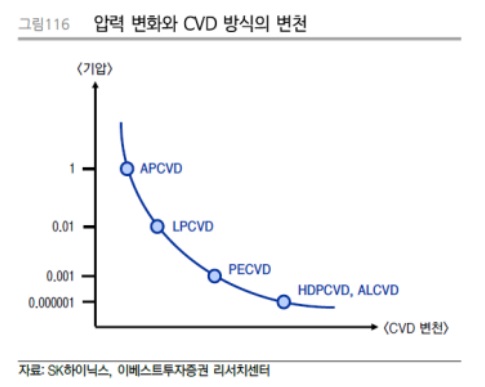

※트랜지스터 내 CVD 증착 보기

※메모리반도체 내 증착공정

5-3) 증착 공정에 쓰이는 전구체

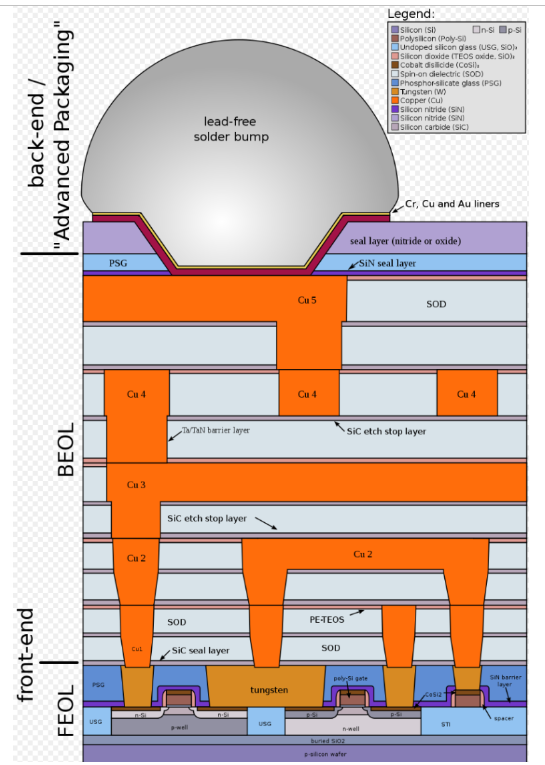

6) 금속배선(BEOL)

6번째 공정이라고 해서 다른 공정처럼 단일적인 공정이 아니다, 금속배선은 엄밀히 말하면 다른 공정들의 종합세트다. 층과 섹터로 나눠진 반도체 칩 하나에서 서로서로의 통로 역할을 하는 금속 형성 공정이다. 그래서 금속배선은 '노광-식각-증착 등' 이 반복되는 것인데, 그러한 공정들을 앞서 설명할 때 트랜지스터 형성에 초점 맞추다보니 다르게 느껴질 수 있다. 실제로 금속배선 부분이 트랜지스터보다 미세화가 덜하므로 기술 차이는 있을 수 있겠다.

그러면 금속배선에 대해 알아보기 전에, 반도체 칩의 구조를 다음 그림으로 다시 한번 살펴보자.

front-end: 트랜지스터 및 셀, 배선 공정이 진행되는 부분.

back-end: 패키징 되는 부분.

FEOL: front-end에서 트랜지스터 및 셀 부분.

BEOL: front-end에서 배선들이 연결된 부분.

금속배선은 이 그림의 BEOL을 형성하는 공정이라고 이해하면 된다. 반도체 미세화를 이야기하다보면 FEOL에 있는 트랜지스터의 크기에만 주로 주목하게 되는데, 금속배선도 소자에 맞춰 미세화되고 특성이 달라지기 때문에 주요한 공정이라고 할 수 있다. 그에 따라 금속배선도 소재와 기술의 발전을 보여주고 있다.

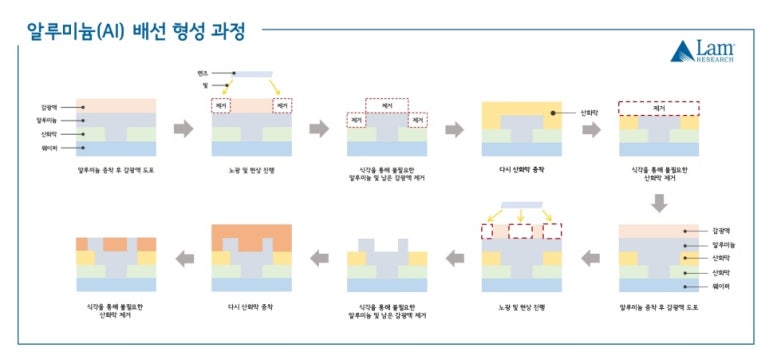

알루미늄(Al) 배선: 알루미늄을 증착 > 노광 > 식각 > 산화막 증착 > 산화막 식각 (반복)

가격이 싸고 전기 전도성이 높고, 증착하기 쉽다. 실리콘과 반응하는 문제가 있어 공정 중간에 보호용(베리어) 메탈을 증착한다.

보통 플라즈마 PVD로 증착한다.

구리(Cu) 배선: 구리 증착 > 산화막 증착 > 노광 > 산화막 식각 > 구리 증착 > 금속CMP로 불필요 구리 제거 > 산화막 증착 (반복)

알루미늄보다 전기 저항이 낮아 빠른 디바이스 속도가 가능하다.

건식식각이 어려워 다마신공법을 사용한다. 기존 알루미늄은 알루미늄 자체를 식각하는 거라면, 다마신은 유전체를 식각하고 빈자리를 구리로 채워 넣는 것이다.

다마신공법: 구리 자체를 식각하지 않고, 유전체(산화막)를 증착하고 유전체를 식각하여 빈 부분(트렌치와 비아 홀 패턴)에 구리를 채운다. 비아홀은 싱글다마신일때는 W(텅스텐)으로, 듀얼다마신일떄는 Cu로 채운다. 주로 듀얼 사용. 그리고 불필요한 구리는 식각이 아니라 CMP로 제거한다.

보통 PVD로 증착된다.

텅스텐(W): 게이트형성 및 금속 컨택으로 쓰이며 낸드 증착에 많이 쓰인다. 텅스텐이 다른 금속 대비 갭 필 특성 및 내열성이 좋아 '트랜지스터-금속'의 중간역할을 한다고 보면 된다. 여기서 말한 텅스텐은 WF6로이다. 보통 CVD로 증착된다.

티타늄(Ti)/티타늄나이트나이트(TiN): 베리어메탈에 주로 쓰이며, 보통 ALD로 증착된다.

코발트: 반도체 공정이 싱글나노로 넘어오면서 구리가 얇아지고 저항이 증가하는 문제가 생기기 시작했다. 그래서 반도체에서 배선이 얇은 아랫층에 코발트를 채용하고 있다. 그리고 중간층까지는 구리와 혼용해서 사용하고 있다. 보통 CVD로 증착한다.

※배선 공정 용어

베리어메탈: 트랜지스터와 금속 사이 저항 발생 문제로(전력소모 증가), 자연스럽게 비금속에서 금속으로 넘어가게 해주는 것이다. 또는 알루미늄(Al)과 규소(Si)의 반응성을 방지해주는 용도로도 쓰인다. 보통 티타늄(Ti)이나 코발트(Co)를 사용한다.

인터커넥트: 반도체 층과 층 사이를 연결하는 수직 통로.

컨택(접점): 트랜지스터와 배선을 연결하는 영역.

7) 이온주입

금속배선은 BEOL이고, 이온주입은 FEOL에 쓰이므로 이온주입이 금속배선보다 먼저 진행되는 공정이지만, 8대공정에 밀려서 순서가 금속배선보다 뒤에 오게 되었다.

이온주입은 부도체인 웨이퍼(단결정실리콘)에 이온(불순물)을 주입하여 반도체로(NMOS와 PMOS) 만드는 공정이다. 즉, 소스와 드레인에 이온을 주입하는 것이다. 트랜지스터를 형성하는 FEOL에 쓰여 빈도가 낮으며, 증착 공정으로 분류하기도 한다.

이온주입에는 Diffusion(확산)방식과 Implantation(이온주입)방식이 있는데, Diffusion방식은 1000'C로 만들어 도핑하는 것인데 소형칩에는 적합하지 않아 선단칩 대부분에는 Implantation이 쓰인다. Implantation은 이온으로 웨이퍼를 때려 박아넣는것인데, 그러한 과정에서 웨이퍼가 물리적으로 손상을 입는다. 이 손상을 입은 웨이퍼를 안정화시키기 위해 어닐링(담금질)를 해야한다.

어닐링: 웨이퍼를 1100~1150도에서 30초 정도 가열.

Furnace방식: 산화공정에서 본 Furnace. 시간이 오래걸린다.

레이저어닐링(RTA): 산화공정에서 본 RTP와 같은 방식으로, 단시간에 온도를 높여 빠르게 구워주는 방식.

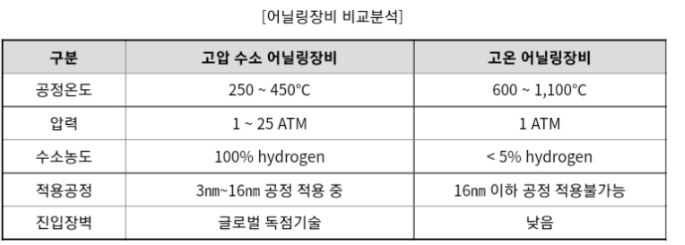

고온수소어닐링: 600~1000'C에서 수소를 넣거나 아르곤+질소를 넣어 하는 방식이다. 고진공에서 진행하며 속도가 느리지만, 수십장씩 넣어 진행하기에 쓰루풋이 좋다.

저온고압수소어닐링: 고압으로 올려 450'C이하에서 진행하는 방식이다. 반도체 팹에서 HKMG 사용빈도가 증가하고 있는데, 메탈은 녹는점이 낮아 다른 어닐링이 어렵기 때문에 저온고압수소어닐링이 필수가 되고 있다.

HPSP 사업보고서

※이온주입의 확산 공정 부품

확산 공정 부품들은 주로 쿼츠로 만들어진다. 확산공정 부품은 식각공정 부품 대비 ASP는 비싸지만, 회전율이 매우 낮다. 다음 부품들은 다른공정에서도 쓰이며, 산화/이온주입 공정에서 주로 쓰인다.

튜브: 확산 공정 진행시 웨이퍼를 다발로 씌워주는 튜브이다. 마모가 활발한 편이 아니라 3년 정도의 수명을 가진다. 업황과는 무관한 일정 시간마다 교체 수요가 생긴다고 봐야한다.

보트: 반도체 화학반응이 일어나는 공정 중 웨이퍼를 이동 및 보관하는 용기이다. Si나 쿼츠로 만들어진다.

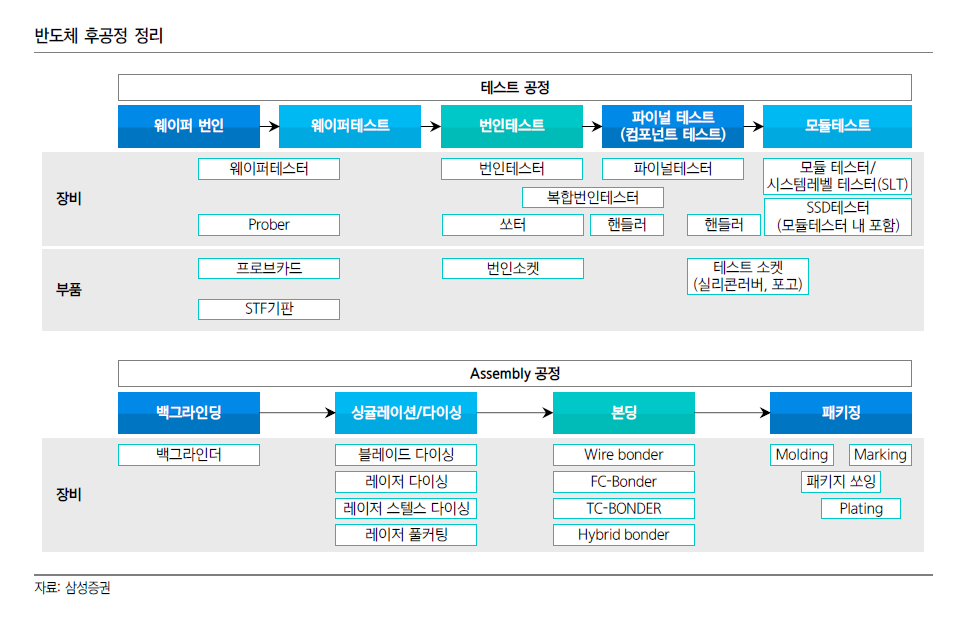

2.2 후공정

1) 테스트

반도체 테스트는 하는 목적과 검사대상에 따라 나눠진다. 목적은 크게 3가지, 온도/속도/동작(신뢰도)가 되겠고, 검사대상은 웨이퍼/패키지/모듈로 나눠진다. 그리고 반도체 칩마다 진행과정이 다 다른데, 예를 들어 PMIC는 패키지 테스트가 따로없고, AP칩은 모든 테스트를 진행함을 볼 수 있다. 본 항목에서는 대부분의 테스트들을 정리했다.

1-1) 웨이퍼번인 테스트

시장이 작고 패키지 번인과 겹치는 부분이 많다.

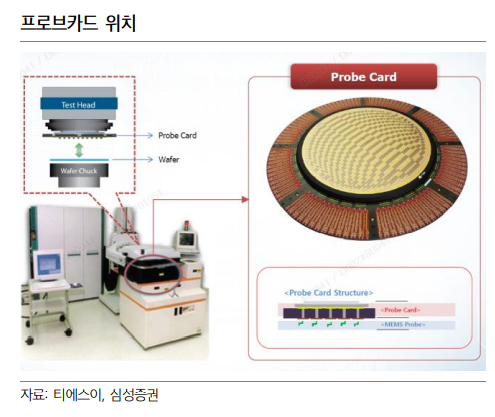

1-2) 웨이퍼테스트(EDS, 프로브테스트)

웨이퍼테스트는 반도체 팹에서 진행되어 그 자리에서 바로 결함을 해결한다. 그래서 전공정으로 분류하기도 한다. 웨이퍼테스트는 웨이퍼와 테스트장비를 이어주는 프로브카드라는 부품을 사용하여 진행되는데, 웨이퍼의 칩 배열마다 다르기 때문에 커스터마이징 부품이며 타입이 크게 두가지로 나뉜다.

MEMS타입: 메모리에 주로 쓰이며, D램이 핀수가 더 많아 기술장벽이 높다.

STF기판: MEMS 프로브카드에 들어가 지지체 역할을 하는 기판.

VERTICAL타입: 비메모리에 주로 쓰인다.

1-3) 패키지 번인테스트

여기서부터는 반도체 다이를 잘라 패키징된 후 진행하는 테스트다. 번인테스트는 반도체에 온도와 전압을 가해 스트레스를 주어 잠재적인 불량을 유도하는 테스트다. 번인장비는 크게 D램용, 낸드플래시용, 로직반도체용으로 나뉜다. 번인장비에는 번인소켓이라는 부품이 들어가는데, 보통 파이널테스트 소켓이나 모듈 소켓을 제조하는 업체가 번인소켓도 제조한다.

번인테스트를 진행하는 과정에서 쏘팅을 하는데, 쏘팅은 웨이퍼에 필요없는 부분(주로 후면)을 갈아내고, 분류하는 과정이다. 그러한 장비가 쏘터이다.

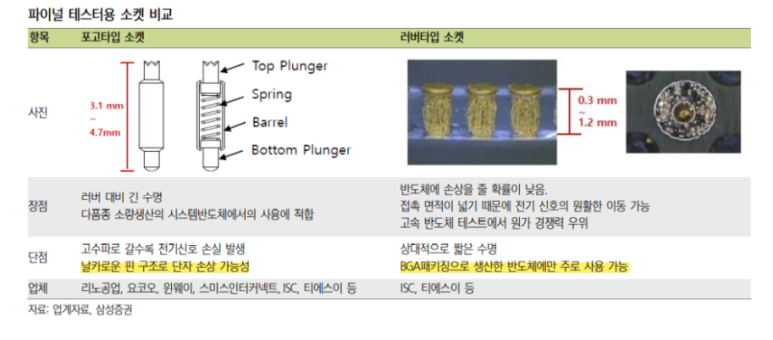

1-4) 파이널 테스트

기존에는 반도체 테스드들 중에 최종으로 진행되어 파이널테스트라고 했지만, 최근에는 모듈 탑재 후에도 테스트를 진행하는 추세라서 이름에 의미가 있지는 않다. 파이널테스트에는 반도체 칩을 탑재하는 소켓이 필요하다.

포고소켓: 비메모리용으로 쓰이며, 러버소켓 대비 피치가 더 작아 미세화에 강점이 있다.

러버소켓: 메모리용으로 자주 쓰였지만, 최근 반도체 패키지들의 I/O 증가로 러버소켓의 사용도가 증가하고 있다.

1-5) 모듈 테스트(SLT)

메모리를 모듈화(DIMM, SSD), 비메모리를 PCB보드에 탑재한 후에 진행하는 테스트다. 반도체 칩 미세화와 어드밴스드 패키징으로 인해 결함을 발견하기가 어려워지고 있다. 그에 따라 모듈테스트는 최종테스트라는 점에서 더더욱 주목받고 있다.

2) 패키징(어셈블리)

패키징은 만들어진 반도체 칩이 외부로부터 전력을 받거나 신호를 주고 받기 위해 통로를 형성하는 공정이다. 반도체 보호의 목적도 있지만, 신호 전달에 있어 효율적인 구조를 형성하기 위함이 크다.

패키징을 알아보기에 앞서, 대부분의 반도체 칩들은 다음과 같은 과정을 거쳐 메인보드에 실장된다. 자세한 내용은 3. 기판 및 PCB 항목에 정리되어있다.

싱글칩 패키징 or 멀티칩 패키징: 칩 to 패키지기판

PCB에 실장: 칩 to PCB, 패키지기판 to PCB

메인보드에 실장: 다수의 PCB to 메인보드

(여기서 말하는 패키지기판은 패키지 섭스트레이트를 말한다. 그리고 메인보드도 PCB의 일종이기 때문에 PCB 실장에서 끝나는 경우도 있다)

패키징도 반도체 칩이나 실장하는 기판의 종류에 따라 패키징 방식이 다를 수 밖에 없다. 특히. FOWLP나 이종접합패키징 같은 경우 더더욱 그러하다. 본 항목에서는 통상적으로 이용되는 공정들만 다루었다.

2-1) 백그라인딩

백그라인더로 웨이퍼의 후면을 얇게 갈아내는 공정이다. 기존에는 백그라인딩으로 그쳤지만, 패키징단에서 배선과 같은 추가적인 공정이 생기면서 CMP도 같이하는 추세다.

2-2) 다이싱

다이싱 장비로 웨이퍼를 개별 단위로 잘라내는 공정이다. 다이싱 장비 종류는 다음과 같다.

블레이드 다이싱: 8인치 웨이퍼에 주로 쓰인다.

레이저 다이싱: 두께가 100um 이하인 12인치 웨이퍼에 쓰인다.

플라즈마 다이싱: 두께가30um이하인 12인치 웨이퍼에 쓰인다. 속도가 빠르다.

2-3) 본딩(다이어태치)

본더를 이용하여 패키지 기판에 칩을 붙여 고정하는 공정이다. 본딩 종류는 다음과 같고, 하이브리드 본딩 및 TSV 기술에 대해서는 5.3어드밴스드 패키징에 정리했다.

와이어본딩: 금이나 구리로 연결한다.

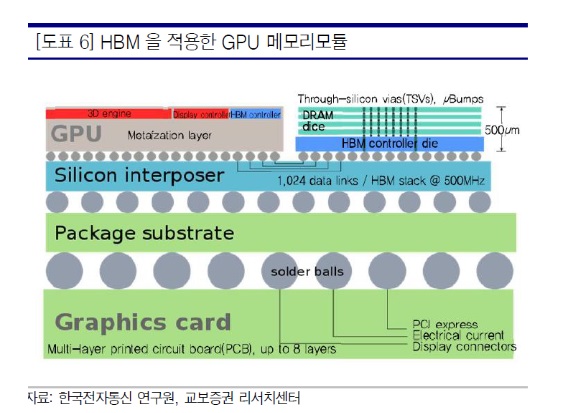

플립칩본딩: 증착/포토/식각 공정을 거쳐 패턴을 형성하고 범프를 붙이는 방식이다.

REFLOW: 칩의 범프와 기판에 열을 가해 범프와 기판의 접착력을 높이는 공정이다. 오븐에 넣어 열을 가하므로 생산성이 높다. 하지만 열손상가능성이 커서 150㎛이상의 범프에서만 적용된다.

TC본딩: 기존 REFLOW 공정에서는 Cu-pillar 범퍼 본딩을 할 때 구리가 얇으면 열에 의해 구리기둥이 녹는 문제가 발생한다. 그래서 구리가 얇을 때는 칩과 기판 사이에 전도성페이스트나 필름을 넣어 열압착하는 TC본딩을 적용하기 시작했다. HBM의 TSV공정에도 주로 쓰인다.

2-4) 몰딩: 반도체 칩을 물리적/화학적 충격으로부터 보호하기 위해 EMC(에폭시 몰딩 컴파운드)로 감싸주는 공정이다.

2-5) 마킹: EMC로 포장된 반도체 칩 위에 제조사, 제품명 등을 기록하는 공정이다.

2-6) 쏘잉: 칩이 장착된 반도체 기판을 PCB에 실장가능하도록 분리하는 공정이다.

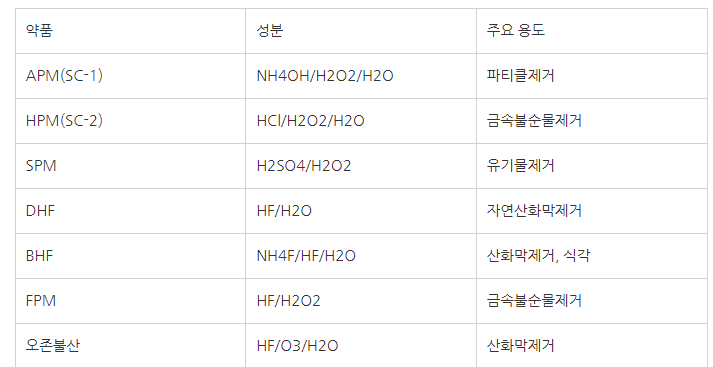

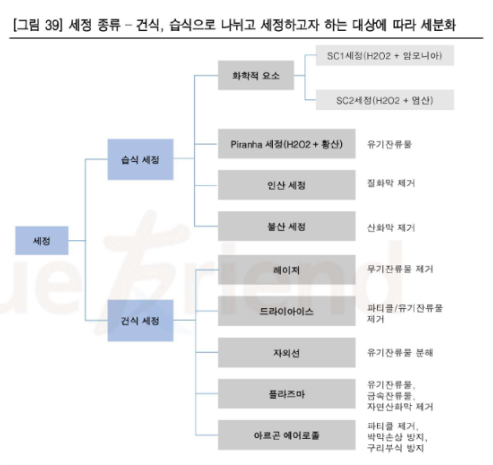

2.3 기타

1) 세정

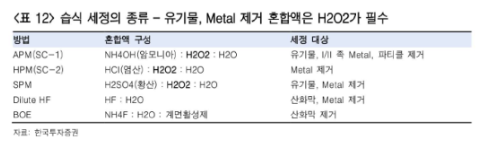

세정공정은 식각, CMP, 확산 등의 공정에서 생긴 오염물질을 제거하는 공정이다. 공정과 공정 사이 자주 진행되어 반도체 제조 공정의 1/3을 차지한다. 세정은 크게 습식세정과 건식세정으로 구분되며 아직까지는 습식세정 비중(70%)이 크다.

습식세정: 과산화수소 등의 세정 용액을 이용하는 방식이다. 습식 세정 후에는 린스와 건조공정이 필요하지만, 비용이 적게 들고 공정 방식이 간단하다.

건식세정: 플라즈마, 레이저, 드라이아이스, 자외선 등을 이용하는 방식이다.

H2O2=과산화수소

습식세정에는 대부분 H2O2(과산화수소)가 필요하다. 반도체 미세화에 따라 정밀도가 필요해지면서 습식세정보다 건식세정의 빈도가 높아지고 있다.

2) PR STRIP

노광과 식각 공정 이후 잔여 PR을 제거하는 공정이다. 포토 공정에서 현상액을 이용해 PR을 제거하는 것은 패턴을 새기기 위함이고, PR STRIP은 웨이퍼를 깨끗이 하는 작업이다. PR은 건식식각 및 이온주입 과정에서 화학적 성질이 바뀌기 때문에, PR STRIP은 건식식각 및 이온주입 후 진행할 경우 O2플라즈마로 상부 PR을 먼저 제거해주고 진행해야한다.

3) 세정/코팅

1)번 항목에서 본 세정은 반도체 팹에서 이뤄지는 웨이퍼 세정을 의미하는 것이고, 여기서 말한 세정/코팅은 반도체 제조장비들에 들어가는 부품 세정이다. 부품 세정/코팅은 주로 외주업체에 맡기며, 세정/코팅을 하면 부품의 수명이 연장되어 부품 소모를 줄일 수 있다. 이러한 세정/코팅 기업들은 세라믹, 쿼츠, Si 등 반도체 관련 소재들에 대한 기술력이 있어야 하므로, 장비부품을 제조하는 업체들이 같이 하는 경우가 많다.

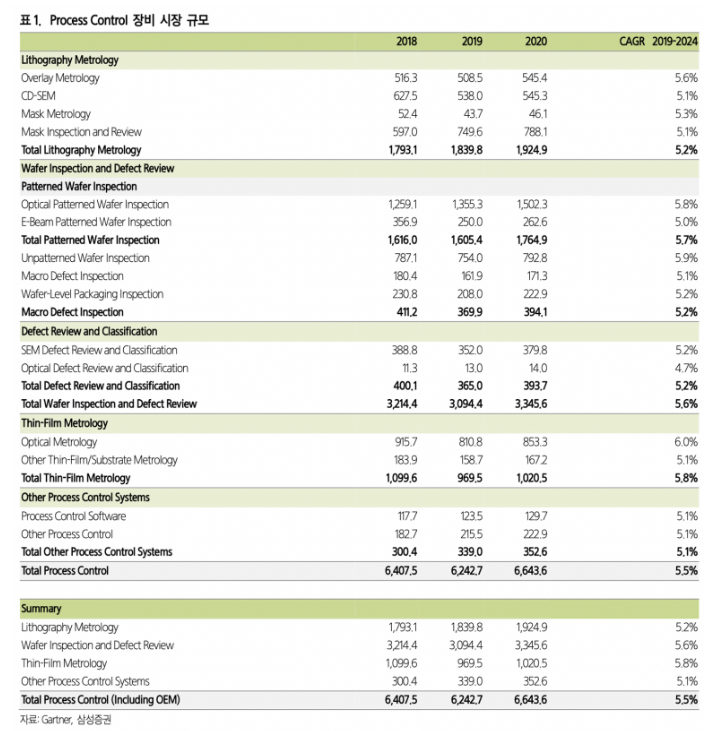

4) 공정제어(검사 및 계측)

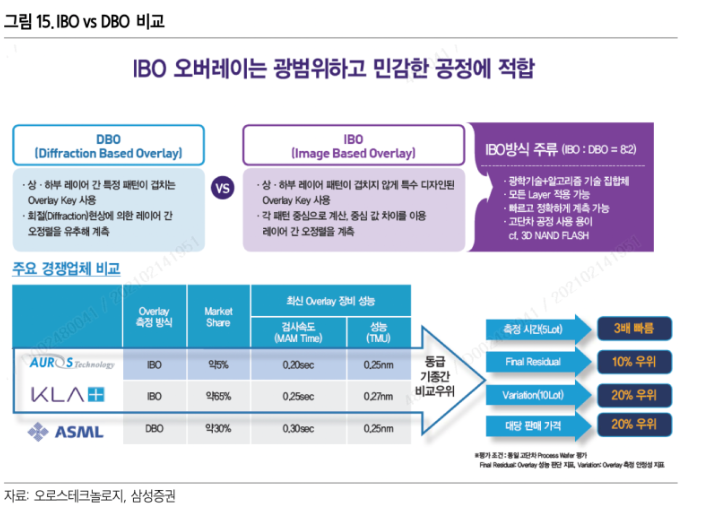

오버레이 계측: 반도체는 트랜지스터 및 배선을 형성하며 레이어를 쌓아 올린다. 적층을 하는 과정에서 균형이 맞도록 쌓아야하는데, 이 때 기준을 잡아주는 것이 오버레이 KEY다. 포토공정에서 진행되며, IBO방식과 DBO방식이 있다.

CD계측: 회로선폭을 계측한다. 포토 공정 후 측정하는 DCD와 식각 공정 후 측정하는 ECD, 2가지로 구분된다.

Thin-film계측: 박막을 계측한다. 모든 공정에 전반적으로 다 사용되는 공정제어다.

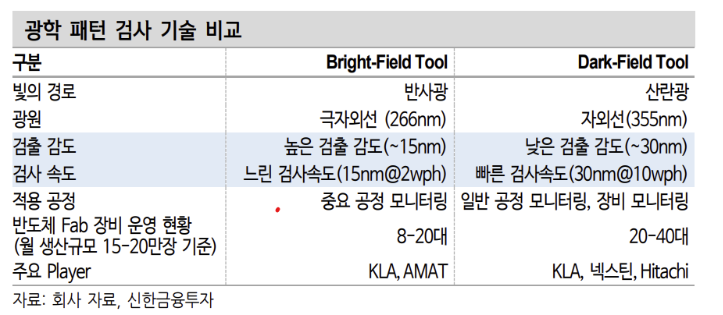

웨이퍼패턴 결함 광학검사

다크필드: UV를 이용해 빠른속도로 검사하며 검출감도가 낮다. CMP, 이온주입, 증착공정에 주로 사용한다. 70% 비중을 차지한다.

브라이트필드: DUV를 이용해 속도는 느리지만 검출감도가 높다. 노광 및 식각공정에 주로 사용된다.

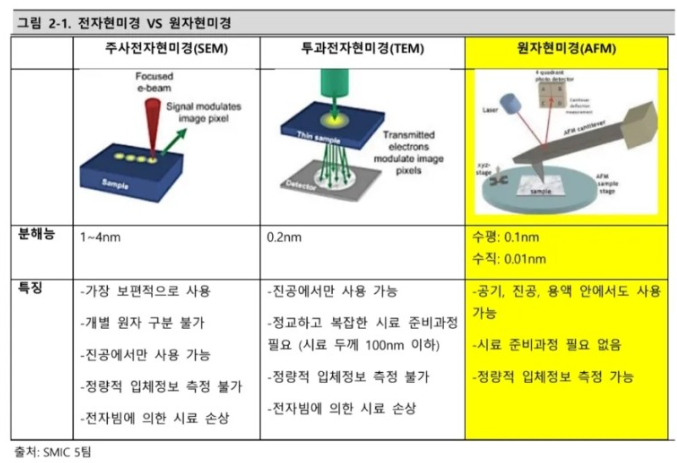

주사전자현미경(SEM) 및 투과전자현미경(TEM): 웨이퍼 투입 전, CMP공정 후, 식각 공정 후에 defect를 찾기 위해 주로 쓰인다. 회로선폭 검사에도 쓰인다.

원자현미경(AFM): 전자현미경으로 측정이 불가능한 미세구조를 관측가능한 현미경이다. 0.01nm까지 측정이 가능하다.

외관검사: 패키징 된 반도체의 외관을 검사하는 것으로, 후공정 발전과 함께 수요가 늘 것으로 보인다.

5) 서브(+인프라)

반도체 공정에 필요한 서브장비들은 다음과 같다.

OHT: 반도체 공장의 천정과 벽면에 달린 레일을 타고 이동하면서 웨이퍼가 담긴 FOUP를 이동시킨다.

FOUP: OHT를 통해서 웨이퍼를 이동시킬 때 웨이퍼를 담는 용기. 반도체 자동화 공정에 있어 쓰임이 많다.

핸들러: 반도체 테스트 공정에서 주검사장비로 칩들을 공급해주고 양품과 불량품들을 분류해주는 자동화장비이다. 메모리용은 한 번에 많은 양(para)을 처리하는것이 중요하고, 비메모리는 분류와 분류 사이(인덱스타임)가 얼마나 짧은지가 중요하다. 비메모리용 핸들러 시장이 2배 크다.

CCSS: 반도체 제조 공정에 필요한 케미칼을 투입하고 분배하는데 사용된다. 탱크, 펌프, 밸브 등으로 이뤄져있다.

스크러버: 반도체 제조공정에서 배출되는 유해가스를 정화하는 장비이다.

클린룸: 건물 내부의 환경 형태가 아주 깨끗한 상태로 유지되는 것. 온도와 습도를 최적화시켜 먼지유입을 차단하는게 중요하다. 핵심은 필터와 공기순환 시스템이다.

칠러: 웨이퍼 공정 환경 최적화를 위해 필요한 온도조절장비다.

진공펌프: 반도체 공정의 대부분은 진공에서 이뤄진다. 다만 진공도가 각각 다르기 때문에 각기 필요한 펌프의 성능은 다르다. 예를들어, EUV노광기에 필요한 진공펌프는 스펙이 매우 높아 현재 1곳만 납품중이다.

세라믹히터: 웨이퍼를 가열하는데 쓰인다.

ESC: 반도체 제조 공정 중에 웨이퍼를 전기적으로 고정시키는데 사용된다.

Descum: 반도체 후공정 과정 중 찌꺼기를 제거하는 장비.

Dispenser: 언더필공정에서 레진, 에폭시를 채워주는 장비.

(공정 공부만 해도 즈응말 어렵다. 그렇기 때문에 반도체 기업을 투자할 때, 기업의 유기체적 움직임을 보는게 크게 의미가 없는 것이다. 기술장벽 자체가 높아서 그것만 뚫어도 기업에게 엄청난 해자를 주기 때문이다.)

3. 기판 및 PCB

(용어가 혼재되어 쓰이다 보니, 정리하기 제일 조심스러운 부분...따끔히 지적해주시길 ㅠ)

기판 및 PCB가 사실상 후공정의 '패키징' 및 '모듈화'의 일부인 것인데, 영역이 워낙 넓어 따로 빼서 본 항목에 정리했다.

사실상 PCB도 기판을 의미하기는 하지만, 투자자들 사이에서는 용어가 혼용되어 사용된다. 우리가 주목하는 어드밴스드 패키징이니~ 차세대 기판이니 하는것들은 보통 패키지 섭스트레이트를 말하는 것이고, PCB는 그러한 기판 또는 칩을 탑재시키는 초록색 판떼기를 말한다(그래서 본 포스팅에서는 '패키집섭스트레이트=패키지기판', 'PCB=초록색판떼기'라고 생각하면 된다). 이렇게 단계별로 패키지를 하는 이유는, 반도체칩의 미세한 I/O를 효율적으로 밖으로 끄집어내는 동시에 보호하고자 함이 크다.

PCB는 기술 진입장벽이 낮아 중국 업체들이 레거시 제품에 대해 저가공세를 한지가 오래되었고, 국내업체들은 대부분 철수하여 소수 업체만 남았다. 그래서 본 포스팅에서는 패키지 기판을 중점적으로 다루고자 한다.

3.1 PCB에 대해

PCB는 인쇄회로기판으로 모든 전자제품에 들어가 있다. PCB는 구리로 만들어진 CCL과 절연층인 PREPREG로 이뤄진다.

PCB를 패키지 섭스트레이트이나 반도체 칩과 연결하는 방식은 크게 두 가지가 있다.

리드프레임: 반도체 칩에 와이어본딩을 해서 리드프레임으로 연결해서 바로 PCB에 꽂는 방식이다. 패키지 섭스트레이가 따로 없다. 2. 리드프레임 항목에 자세히 기술했다.

솔더볼: PCB와 패키지 섭스트레이트간의 I/O를 늘리기 위해 솔더볼로 연결하는 방식이다. 접합부가 선에서 면으로 되었다고 보면 된다.

자주 쓰는 PCB는 다음과 같다.

HDI: 스마트폰/노트북 등 소형 전자기기용 고밀도 다층 회로 기판이다. SLP에 시장을 뺏기나 싶었는데, 인터포저를 도입해서 현재는 '인터포저+HDI'가 주류이다.

SLP: HDI에 MSAP공법을 접목한 기판이다. 회로간 선폭 및 전체 면적을 축소할 수 있다. SLP가 적용된 층이 많을수록 면적 효율이 좋아진다.

FPCB(Fexible PCB): 기존의 Rigid PCB와 다르게 유연하게 휘어지는 PCB다. 디스플레이 및 스마트폰에 주로 쓰인다.

RFPCB(Rigid FPCB): Rigid한 부분과 Flexible한 부분이 같이 들어가있는 PCB다.

MLB: 여러층으로 구성되어 있는 PCB다. 주로 통신용, 서버용으로 쓰인다. 최근 기술로는 26층까지 적층이 가능하다.

메모리모듈PCB: 패키징된 메모리 반도체를 모듈화하는 PCB다. 어플리케이션마다 형태와 이름이 다르다.

3.2 리드프레임

리드프레임은 패키지 섭스트레이트라는 개념이 명확히지기 전에 생긴 패키징 방식이다. 리드프레임 자체가 패키지 기판 역할을 하면서 PCB와 칩을 연결해준다고 보면 된다.

리드프레임은 레거시제품으로 가격도 저렴하고 안정성이 높아 아직까지 저가형 칩에 많이 사용된다. 대표적인 반도체 칩이 MCU이다.

리드프레임 생산 방식에는 크게 2가지 방식이 있는데, SLF방식과 ELF방식이다.

SLF: 초정밀 금형으로 찍어서 생산하는 방식으로 대량생산에 적합해 가격은 낮지만 품질도 낮다. SOP/DIP/SO/QFP의 패키징이 SLF방식을 주로 사용한다.

ELF: 회로패턴을 약품으로 식각 성형하여 품질 좋은 리드프레임을 생산할 때 쓰는 방식이다. QFN패키징이 ELF방식을 주로 사용한다.

다음은 앞서 나온 리드프레임 방식 패키징들을 나열한 것인데, 기판이라는 개념과 리드프레임 방식 그 사이라고 이해하면 될 듯 하다. 말보다는 그림으로 보는게 차이를 이해하는데 도움이 될 듯 하다.

DIP: 직사각형 모양으로 내부회로와 연결도선이 수직으로 붙어있다. 칩과 리드프레임은 와이어본딩으로 연결되어 있다.

SOP: 리드프레임 위에 칩을 올리고 . TSOP와 SSOP로 나뉜다. t

QFP: L리드가 나와있는 형태. 우리가 아는 거미같이 생긴 칩이다.

QFN: 튀어나오는 리드프레임이 없기 때문에 작은 모바일기기 및 MCU에 주로 쓰인다.

3.3 패키지 섭스트레이트

1) 반도체 칩과 패키지 섭스트레이트 연결 방식

WB와 FC라는 약자는 패키지 섭스트레이트 명칭에 쓰여 특징을 알 수가 있다.

와이어본딩(WB): 얇은 Gold wire 를 통해 연결.

플립칩(FC): Solder bump를 통해 연결. WB대비 많은 수의 I/O를 형성할 수 있어, 하이엔드 칩들은 대부분 FC 패키지에 실장한다.

※솔더볼과 솔더범프: 솔더볼이 솔더범프보다 크며, 솔더볼은 주로 PCB와 패키지 섭스트레이트 사이의 연결단자를, 솔더범프는 칩과 패키지 섭스트레이트간의 연결단자를 말한다. 솔더범프도 솔더볼로 만든것이기에 그냥 솔더볼이라고 부르기도 한다. 솔더볼과 솔더범프는 크기와 목적에 따라 다음과 같이 구분된다.

SB(솔더볼)

MSB(마이크로솔더볼)

CSM(코어솔더볼)

2) 어플리케이션별 패키지 섭스트레이트의 변화

패키지기판은 기술력 있는 IDM 업체나 OSAT에서 연구함에 따라 새로운 기술이 나오고 그에 맞는 기판들이 나온다. 어플리케이션별로 주류가 되는 기판이 다르기 때문에 무작정 뭐가 짱이다라고 말할 수가 없다. 어플리케이션별로 패키지 섭스트레이트의 발전은 다음과 같다.

D램: BOC > FCBOC

SSD: BOC > FCBOC

모바일 메모리: eMCP

모바일AP: WBCSP > FCCSP(SiP) or FOWLP > 3D FOWLP

로직반도체: 리드프레임 > BGA > FCBGA > 2.5D+FCBGA

RF: BGA > FCBGA > AiP

전장: 리드프레임(QFP) > FCBGA (전장은 개별제어에서 중앙제어로 바뀌면서)

그리고 같은 기판이라 하더라도, 어플리케이션별로 요구되는 면적/층수가 다르기 때문에 기술의 난이도가 다르다. 이제 기판 종류를 나열할 예정인데, 공법의 이름이 그대로 기판의 종류가 되는 경우도 있고 혼용되는 경우가 있어 헷갈리기 쉽다. 그래서 공법에 대해 먼저 공부하고 기판의 종류로 넘어가보자.

3.4 공법

PCB와 패키지 기판도 헷갈리는데, 기판의 공법이름과 기판 종류도 혼용되는 경우가 많다. 공법 자체가 기판 이름이 되는 경우도 있으니 잘 참고하길 바란다.

1) MSAP공법: 기판의 회로선폭을 줄이기 위한 공법이다(30마이크로 이하). 반도체의 고집적화 및 미세화와 관련된 기술들을 기판에 접목시킨 공법이다. SiP, AiP, FCCSP, FCBGA 기판을 제조하는데 쓰인다.

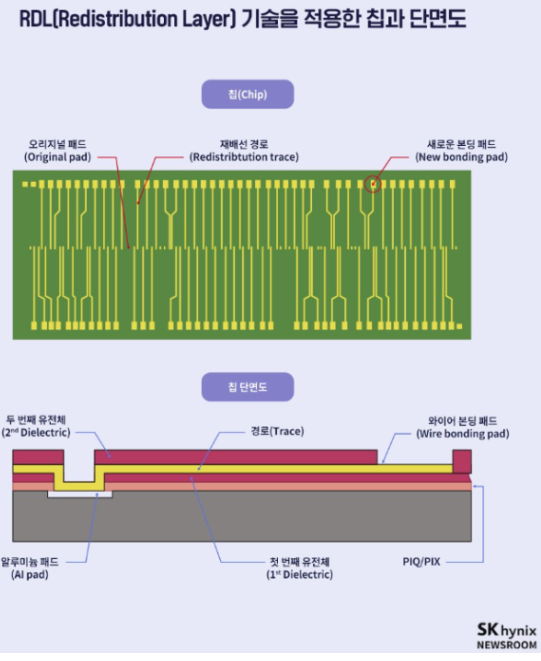

2) RDL: 칩간의 I/O 연결을 위해 칩 중앙에 위치한 본딩 패드를 엣지로 재배열하는 공정이다. 칩의 설계나 구조 변경 없이 칩을 적층할 수 있다. 반도체 팹에서 쓰는 높은 기술력이 필요하다.

3) MCM공법: multi chip module. 각각 패키징 된 칩들이 모여서 범핑이나 와이어본딩으로 연결되는 방식.

4) MCP공법: multi chip package. 하나의 패키징안에서 다이를 적층시켜 공간을 최소화시키는 패키징 방식.

eMMC: 임베디드 기기그를 위해 낸드플래시와 컨트롤러가 통합된 BGA 제품.

eMCP: eMMC에 모바일 D램을 적층 패키징한 제품.

DDP: 메모리소자를 2층으로 적층 패키징한 제품.

5) SiP공법: System in Package. 여러 종류의 반도체 칩을 하나의 패키지로 구성하는 기술이다. 초경량, 초소형에 적합하며 모바일, 카메라모듈, 웨어러블 기기 칩에 자주 쓰였는데, 기술이 발전함에 따라 그 범위가 넓어지고 있다.

6) PoP공법: Package on package. 패키지위에 패키지를 올리는 공정으로, 이종접합 패키징이 등장하기 전에 메모리 칩과 비메모리 칩을 결합하는 대표적인 공정이었다. 패키지와 패키지를 연결할 때 인터포저 PCB를 넣어 연결한다.

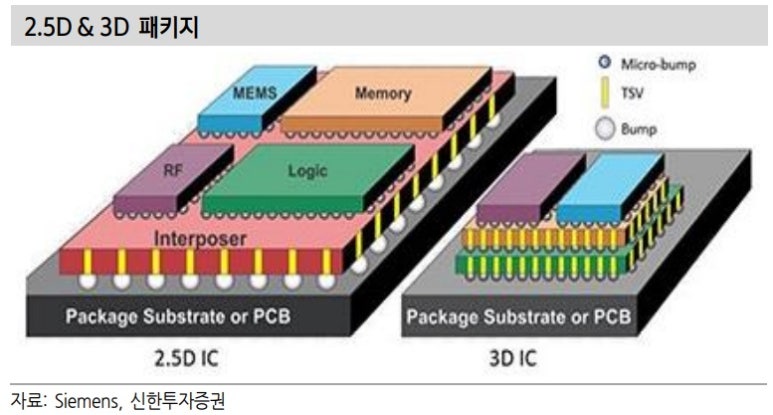

7) 2.5D/3D 구조: 기존의 이종접합 공법들은 와이어본딩 위주로 진행되고, 2.5D/3D는 인터포저와 범프를 이용하여 이종접합이 진행된다는 점에서 차이가 있다. 5.3 항목에 자세히 기술했다.

3.5 패키지 섭스트레이트 종류

1) FCCSP

※CSP: Chip Scale Package. 반도체 칩 사이즈에 맞는 기판들을 칭한다. 보통은 소형기기에 들어가기 위해 쓰이는 기판이다. 와이어본딩으로 연결하면 WBCSP, 솔더볼로 하면 FCCSP이다.

※SCSP: 메모리반도체를 적층할때 쓰이는 CSP기판의 한 종류.

FCCSP는 플립칩 CSP이다.

칩~섭스트레이트: 플립칩

섭스트레이트~ PCB: 솔더볼

패키지 사이즈는 20mm이하, 2~16층으로 작은 사이즈에 집적화를 위해 만들어진 기판으로 주로 모바일AP로 많이 쓰인다.

2) FCBGA

※BGA: Ball Grid Array. 솔더볼이 배열되어있는 기판들을 칭한다. 와이어본딩으로 된 BGA는 WBBGA이다. 현재 대부분의 패키지섭스트레이트는 PCB와 솔더볼로 연결되기 때문에, BGA 가 주류라고 볼 수 있다.

※LGA: Land Grid Array. 네모난 형태의 랜드가 배열되어있는 기판. BGA로 인해 현재는 잘 사용하지 않는다.

※PGA: Pin Grid Array. 핀이 배열되어있는 기판. BGA로 인해 현재는 잘 사용하지 않는다.

FCBGA는 플립칩 BGA이다.

칩~섭스트레이트: 플립칩

섭스트레이트~ PCB: 솔더볼

패키지 사이즈는 25~70mm, 층수는 6~22층으로 어느기판이 그렇듯 대면적화/다층화에 따라 기술력이 나눠진. FCBGA는 ABF라는 특수 절연층으로 만들어지는데, 아지노모토라는 일본 기업이 독점 생산중이다.

서버 > 네트워크 > PC > 전장, 앞에서부터 기술력이 높다고 보면 된다.

3) WLCSP (WLP)

패키지 섭스트레이트를 없애고 웨이퍼상태에서 솔더볼을 부착하는 패키징이다. 기존의 패키지기판들은 웨이퍼에서 칩들을 개개별로 다이싱하고 각각 패키징하는 것인데, WLP는 웨이퍼 상태에서 바로 캐리어 역할을 하는 웨이퍼를 붙여 진행한다. 그래서 패키지 기판의 종류가 아니며, 반도체 공정을 이용하기 때문에 반도체 팹에서 직접한다.

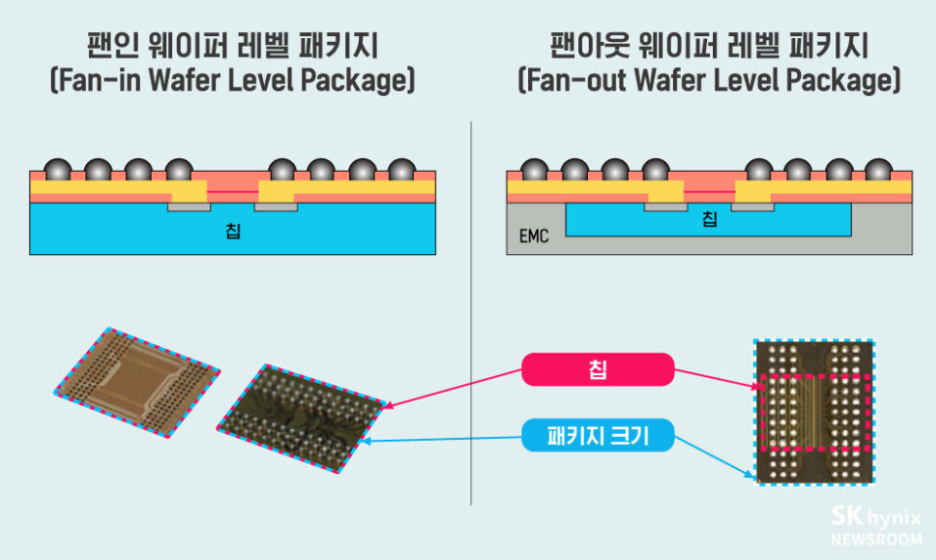

FIWLP(팬인)와 FOWLP(팬아웃)으로 나뉘는데, 팬인은 다이싱을 하지 않고 그대로 패키징하여 칩크기=패키지크기가 되는 것이고, 팬아웃은 다이싱을 하여 재배치하기 때문에 칩크기<패키지크기 가 되는 것이다. WLP뿐만 아니라 다른 패키지도 팬인/팬아웃으로 나뉘는 경우가 있는데, 팬인은 크기를 줄이는데 용이하고 팬아웃은 I/O를 늘릴 수 있다는 장점이 있다.

4) FOWLP/PLP (Fan Out Wafer Level Package/Panel Level)

FIWLP의 아쉬운 I/O로 등장하게 된 패키징이다. 솔더볼의 미세화가 쉽지 않기 때문에 FIWLP의 I/O 수에 한계를 맞이하고, 그로인해 45nm 이하 반도체 칩에 적용하기가 어려웠다. FOWLP는 더 넓은 캐리어웨이퍼에 RDL을 적용해 더 많은 솔더볼을 부착할 수 있다. 현재 FOWLP는 RF/AP/PMU 기판 시장을 빠르게 침투하고 있으며, 특히 모바일향으로 많이 쓰이는 FCCSP를 위협하고 있다.

FOPLP는 FOWLP와 비슷한데 WLP가 원형의 웨이퍼에 패키징되는 반면, PLP는 사각형의 패널에 패키징하는 것이다. 칩이 사각형 모양이다보니 패키지웨이퍼를 거기에 맞춰서 공간효율성을 올리기 위함인데...반도체공정의 대부분 장비들은 원형웨이퍼에 맞춰져있기에 PLP는 장비호환성에 있어 비효율적이다는 이야기가 많다. 퀄컴의 PMIC칩 FOPLP를 채택하기도 했다.

5) FCBOC

D램용 FCCSP라고 보면 된다. 컴퓨터, 노트북, 서버, SSD, 그래픽카드용 D램 패키지로 쓰인다.

칩~섭스트레이트: 플립칩

섭스트레이트~ PCB: 솔더볼

6) SiP

칩~섭스트레이트: 아무거나

섭스트레이트~ PCB: 솔더볼

SiP공법이 적용되는데 최적화된 패키지다.

7) RF-SiP

RF에 특화된 SiP이다. 로직칩과 수동소자(저항, 콘덴서 등)이 결합되어 패키징된다. 스마트폰, 웨어러블 기기, IoT에 들어가며 RF부품들(PA, BAW Filter, SAW Filter, FEM)로 쓰인다.

8) AiP

Anntena in Package. SiP공법으로 안테나와 트랜시버를 집적화시킨 패키징이다. RF-SiP의 연장선이라고 보면 된다. 초고주파 대역을 사용하는 스마트폰, 태블릿은 기기당 AiP모듈이 2~4개가 배치된다. 복잡한 신호들을 빠르게 전달해야하는 5G 환경에서 소형 전자기기 필수적인 패키지다.

4. 반도체 사이클 및 주가

최근에 상장한 몇몇 기업들을 제외하고는 대부분의 기업들이 삼성전자 및 SK하이닉스와 같이 국내 반도체 시장을 함께 해왔기 때문에, 메모리 사이클에 따라 센티가 크게 변한다. 그리고 주식시장 내 반도체 섹터는 성숙 산업에 속하기 때문에, 각 소부장 영역에 있어 고인물 종목들이 많다.

그에 따라, 특정 테마나 트렌드에 민감하게 관련 종목들이 반응하는 행태를 자주 볼 수 있다. 예를 들어, 두 양대산맥(삼성전자, SKH)의 소소한 움직임 하나가 관련 밸류체인들의 주가를 건드린다던가, .EUV, 인프라, OSAT 등 각각의 키워드에 관련 기업들의 주가가 움직인다.

먼저, 반도체 사이클부터 알아보자.

4.1 반도체 사이클

내용은 메모리 사이클을 위주로 정리했지만, 반도체라는 아이템 자체가 경기에 민감하기 때문에 비메모리 사이클도 크게 다를 바가 없다. 진폭이 낮고 빈도가 메모리 대비 낮기 때문에 없는 것처럼 보이지만, 비메모리 투자도 메모리 사이클을 참고하여 투자하면 추가적인 멀티플 상승을 노릴 수 있다.

메모리에서 NAND는 아직까지 경쟁자가 좁혀지지 않았지만, D램은 삼전/SKH/마이크론 3개의 업체로 과점형태를 띄고 있으며, 이 3개 업체가 NAND도 하고 있기 때문에 D램에서 얻은 이익으로 NAND 시장도 선두하고 있다고 볼 수 있다.

1) 치킨게임

1980년대부터 반도체 업체들이 대거 등장하면서, 메모리 업체들도 경쟁이 치열해졌다.

2007년: 키몬다 파산 후 9개 업체 생존.

2009년: 삼전 제외 모든 업체 적자 속에서 SK의 하이닉스 인수, 마이크론의 엘피다 인수로 정리.

~: D램 3사 과점, 낸드 6사 경쟁 중. CPU 2사, GPU 2사, AP 5사, DDI 5사, FPGA 2사, CIS 5사, RF 2사, 선단파운드리 3사 독과점 중.

2) 슈퍼사이클의 등장

과점화된 시장에서 수요가 터지면 공급업체는 황금기를 맞는다. 공급을 일시적으로 올리기는 어렵고, 전방업체들 또한 쇼티지에 대한 두려움으로 P는 급상승한다. 물론 하락사이클도 그와 같은 특성을 가지고 있다 (공급을 줄이기는 어렵고, 전방업체들의 CAPEX는 감소 및 더 싸질거라는 생각).

2009~2013년: 반도체 종합 세트인 스마트폰이라는 어플리케이션 등장.

2017~2018년: 데이터센터(서버) 수요 급증.

2020~2021년: 언택트로 IT기기 수요 증가 및 데이터 처리량 급증.

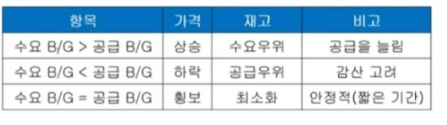

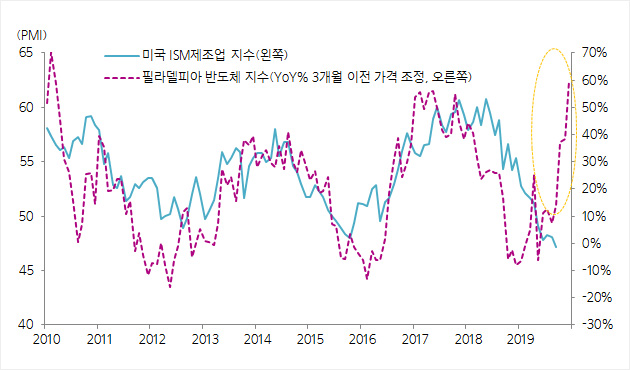

3) 사이클의 시그널

반도체 수요는 장기적으로 상승하지만, 수요와 공급의 미스매치로 크고 작은 사이클이 생기면서 선행하는 지표들이 시장에 알려졌다. 주식 시장에는 '법칙'이 없기 때문에 참고로만 봐야하며, 반도체 전방이 경기에 민감하다 보니 예상치 못한 NEW 어플리케이션, 거시경제, 지정학적 이슈로 사이클이 급변하고는 한다.

투자자들이 자주 보는 시그널들은 다음과 같다.

빅테크업체들의 재고자산

반도체 팹의 재고자산

반도체 팹의 CAPEX

거시경제 관련 지표(글로벌 유동성, 노동지표)

미국ISM 제조업 지수

중국 IT 수요

현재 자주 언급 되는 반도체 사이클의 뷰는, '바닥 확인' 이다. 반도체 수요는 예상이 어렵기 때문에 반도체 팹 업체들의 의미있는 감산 발표나 재고자산 피크를 통해 바닥을 확인하는 것이다. 턴어라운드 시점을 찾기는 어렵지만 바닥에 사고 버티면 수익이 된다 라는 주의이다. 이러한 사이클 특성은 과점화된 메모리 시장에서 더욱 더 강하게 나타난다.

그렇다면 다음 슈퍼사이클은 언제올까? 전술했다시피 신의 영역이지만, 사이클에 대해 공부하고 본인만의 관점을 세운 뒤 예측이 아닌 대응을 하면, 지점 투자는 아니더라도 구간 투자를 하는데 괜찮은 엣지를 챙길 수 있을 것이다. 그렇기에 다음 블로거분들의 글들을 참고하여 타당한 근거들을 찾아 본인만의 관점 정립을 추천드린다.

(양파님)

(Lepain님)

(구름님)

(알파카이코노미아님)

(재덕님)

(센텀호랑이님)

(춰릿님)

(선진짱님)

추가로 선두업체들의 분기 컨콜에서 힌트를 찾을 수 있다.

삼전=메모리 업황 및 파운드리 선단공정

SKH=메모리 업황

TSMC=글로벌 팹리스 업체들 선단공정 수요

ASPEED=서버향 반도체 수요

AMAT=반도체 팹들의 CAPEX

ASML=선단공정 진행 상황

엔비디아=AI 시장의 반도체 수요

이비덴/신코=선단 기판들 현황

4.2 비메모리 및 엣지에 대한 프리미엄

우리나라 반도체 산업은 메모리 반도체를 중심으로 발전해왔다. 그래서 삼성전자와 SK하이닉스는 각각 소부장 밸류체인을 꾸려왔고, 그러한 소부장 업체들은 메모리업황에 따라 실적변동이 심했다. 삼전과 SK하이닉스 급의 해외 메모리업체는 사실상 마이크론 밖에 없기 때문에, 메모리 소부장 업체가 마이크론에 대량 납품을 하지 않는 이상 해외 수출에 대한 프리미엄을 주기는 어렵다.

메모리 소부장업체들도 이러한 환경에 질려버리기 시작했고, 초과수익을 내려면 리치마켓의 엣지기술을 보유하거나 비메모리향 역량을 키워 해외수출을 해야함을 깨달았다. 미국/일본/유럽의 탄탄한 기초과학 때문에 그 진입이 쉽지는 않지만, 그 장벽을 뚫으면 인텔 및 TSMC와 직접 거래를 할 수 있어 그러한 업체들에 대한 프리미엄은 최소 PER 15이상이 되기도 한다.

아직까지 메인 공정의 소부장 시장을 뚫은 업체는 거의 없지만, 메인 공정 간 리치마켓 시장을 침투하는 국내 업체들이 늘어나고 있는 추세다.

엣지 기술과 비메모리향 납품으로 인한 멀티플 상승의 대표적인 사례가 다음과 같다(그 해자가 약해지고 있는 기업도 있다)

주성엔지니어링 인텔 납품

HPSP 고압수소어닐링 장비 비메모리향

넥스틴 KLA 독과점 시장 침투

파크시스템스 마스크 리페어장비

피에스케이 비메모리향 장비 납품

리노공업 비메모리향 소켓 납품

한미반도체 후공정 본딩 장비

FST/S&S TECH EUV펠리클 기대감

티씨케이 SiC링 독과점

5. 반도체 트렌드/변화

5.1 반도체 자국화(리쇼어링)

미중분쟁을 기점으로 탈세계화가 일어나고 대부분의 제조업에 있어 리쇼어링이 일어나고 있다. 반도체는 4차 산업의 쌀로 리쇼어링 기조가 더 강할 수 밖에 없다. 하지만 반도체는 설계부터 제조, 소부장까지 모두 강점을 가지기가 어렵고, 그나마 근접한 미국 조차도 첨단 파운드리는 TSMC에 의존하고 있는 상황이다. 이러한 흐름 속에서 대체할 수 없는 기술력을 가진 기업들은 그 격차를 더 벌릴 것이고, 적당한 기술력으로 매출이 발생하던 기업들은 자국 기업들에게 파이를 뺏길 수 밖에 없음을 참고하여 반도체 섹터를 봐야할 것이다.

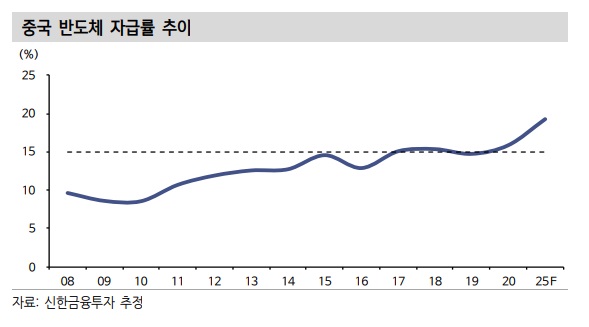

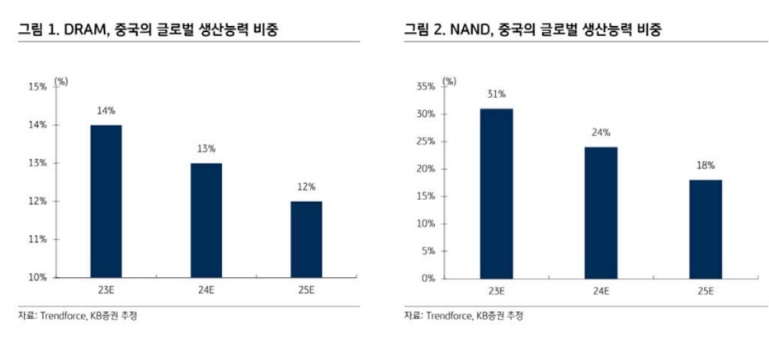

1) 중국

알다시피 중국은 국영기업 위주로 산업을 이끌어가며 정부에서 픽한 산업은 대놓고 밀어준다. 낮은 인건비와 국가의 지원으로 밀어붙인 2010년대 LCD시장을 보면 그 위력을 알 수 있다.

물론 중국이 아직까지는 반도체 강국들과의 기술력 차이가 3년 이상이며, 미국의 규제로 첨단 장비들이 반입 불가한 상황이다. 그럼에도 불구하고 중국은 절대 반도체를 포기할 수 없으며 현 상황에서 최선인, 레거시 팹에서 엄청난 물량을 찍어내려고 한다. 이 물량들이 자국 내 수요를 충당하고 해외로 풀릴 경우 어떤 현상이 생길지 의문이다.

D램의 CXMT, 낸드의 YMTC, 파운드리의 SMIC, 비메모리 팹리스의 하이실리콘 등 그들의 선단 공정 진출 및 웨이퍼 CAPA를 지켜볼 필요가 있다.

CXMT: 19nm

YMTC: 128단(232단 개발완)

SMIC: 7nm

2) EU

유럽은 전세계 반도체 수요의 20%를 담당하고 있지만, 공급능력은 10%밖에 되지 않아 대외 의존도가 높은 곳이다. EU는 그의 심각성을 알고 막대한 자금을 투입하기로 결정했다.

물론 EU내에 규모있는 물량을 소화할 기업은 인피니온, STM 밖에 없는 상황으로, 타 국가의 기업들을 유럽 내에 유치할 가능성이 높다.

인텔은 이미 장기적인 로드맵을 발표했다.

3) 미국

미국은 반도체 본국으로 수 많은 특허를 가졌고, 기술의 원천이 다 지들(?)꺼라고 한다. 그래서 그 영향력이 어마어마하고 사실상 반도체 강국들을 상대로 협박 아닌 협박을 하고 있는 상황이다. 미국은 동맹을 강화하자는 취지로 법안을 내고 있지만, 사실상 중국따돌리기에 가깝고 아메리칸퍼스트를 위한 관세보복전쟁과 양상이 흡사하다.

동맹인지 토사구팽인지는 훗날에 알겠지만, 반도체 기업들 입장에선 미국의 말 한마디한마디에 빠르게 대응해야할 필요가 있다. 미국이 발표한 반도체법은 현재 다음과 같은 큰 틀에서 진행되고 있다.

미국 내 팹 유치

중국 증설 제한

첨단 소부장 및 반도체, 중국 반입 불가

MADE IN CHINA, 고율 관세

현재 반도체 기판에 대해서도 비슷한 규제가 적용될 것으로 보인다.

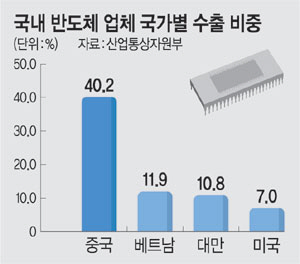

4) 한국

한국은 글로벌 메모리 시장의 70%와 파운드리 18%를 차지하고 있는 반도체 강국이다. 내수시장이 작기 때문에 중국 시장에 수출을 하는 동시에 중국에 팹을 유치하며 성장해왔다.

그렇기에 이번 미중분쟁에 있어 제일 영향을 많이 받을 국가가 한국이지 않을까 싶다. 정부에서는 이미 미국을 픽하는 액션을 보여줬고, 올해 내로 그로 인한 그림들이 그려지기 시작할 듯 하다.

그 중 제일 먼저 보여진 것이, 대만 TSMC에 의존적인 미국이 삼전을 꼬셔 대만/한국 이원화 전략을 펼치고 있는 것 아닐까 싶다.

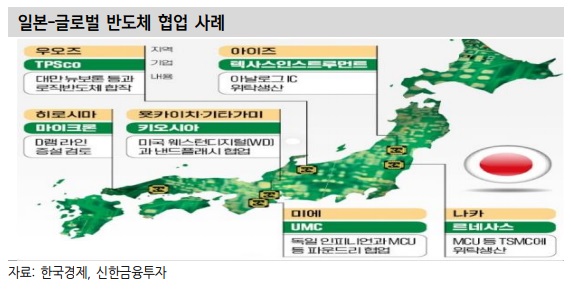

5) 일본

일본은 반도체 소부장에 강하지만 칩 생산에는 약한 국가다. 글로벌로 60%가 넘는 웨이퍼/PR의 점유율이 그것을 보여준다. 반도체 제조 업체는 아예 없는 것은 아니지만 낸드의 키옥시아와 CIS의 소니가 유일한 중견기업이라고 볼 수 있으며, 파운드리의 부재가 크다.

그래서 일본도 자국 내에 해외 반도체 업체의 팹을 유치하고자 노력 중이며, 2021년에 TSMC를 끌어들여 10nm대 팹을 짓기로 결정했다고 한다. 그러한 것들을 봤을 때, 소부장이 약하고 반도체 생산에 강한 대만과 협력을 하여 서로를 보완하는 형태로 강점을 유지할 것으로 보인다.

이미 일본에 팹이 있는 마이크론도 작지 않은 규모로 투자한다고 한다.

추가로, 일본 반도체 기업들의 합작사인 Rapidus의 행보도 볼만 할 것 같다.

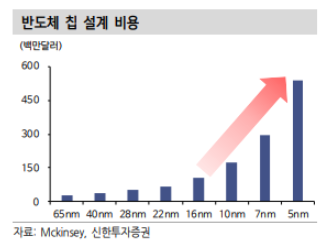

5.2 미세화

반도체는 선단공정으로 갈수록 비용이 증가하는데, 2010년대부터 싱글나노로 들어오면서 증가율이 커지고 있다. 반도체 팹 자체에서 수율을 못 잡는것도 있지만, 그에 따른 소부장 전체가 고난이도의 기술을 필요로 하기 때문이다.

1) EUV

앞서 1.5.(6)노광 항목에서 다뤘기에 여기서는 간단히 정리하였다. EUV노광기는 반도체 칩의 미세화에 있어 매우 중요한데, EUV노광기를 독점하고 있는 ASML의 실적과 멀티플이 그것을 나타내고 있다. 모든 광원들이 그랬듯이, EUV도 새롭게 등장하고 High-NA 버전으로 신제품을 내놓고 다음 광원이 등장할 것이다.

현재 EUV노광기는 High-NA로 들어가는 단계이며, 올해 ASML은 0.55NA 버전을 출시할 예정이다.

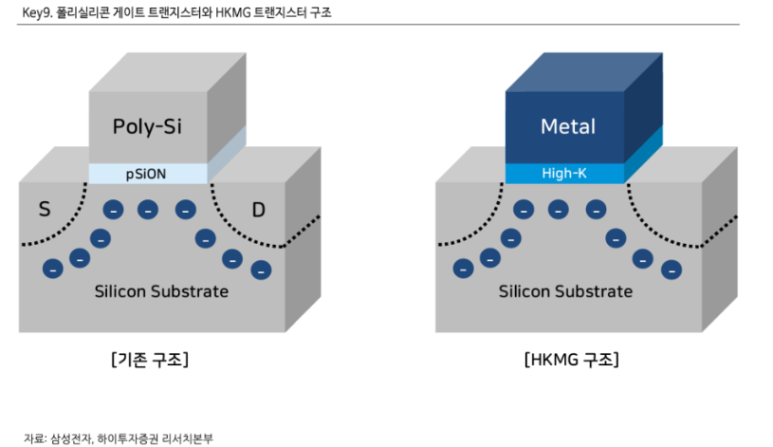

2) HKMG

트랜지스터가 미세화되면서 게이트의 절연막을 담당하는 옥사이드 또한 얇아지고 그로 인해 터널링 현상이 발생하게 되었다. 그 임계점이 45nm이며 이 터널링 현상을 해결하기 위해 유전율이 높은 소재를 채용하게 된 것이다. 그리고 High-k 소재가 채택되면서 게이트의 poly-Si과 맞질 않아 Metal Gate가 채택된 것이라고 보면 된다.

하지만 기존의 HKMG 또한 22nm부터 다시 누설전류가 발생하면서 다른 방법을 모색하게 된다. 그것이 바로 FinFET과 GAA이다(1.5항목 참고). FinFET과 GAA는 아직까지 HKMG의 채택률이 높지 않다.

유전율이 3.9 이상이면 High-k라고 하는데 다음의 소재들이 대표적인 High-k이다.

SiO2(산화실리콘): k=3.9

Al2O3(알루미나): k=7

ZrO2(지르코늄옥사이드): k=22, 현재 제일 많이 쓰는 소재다.

HfO2(하프늄옥사이드): k=24, 지르코늄에서 하프늄으로 넘어가는 추세다.

TiO2(티타늄옥사이드): k=60. 새롭게 주목받는 차세대 high-k물질이다.

ZAZ: 지르코늄과 알루미나를 혼합한 물질. 최종K=25.

D램의 캐패시터에도 High-k가 쓰이는데, 주로 ZrO2를 많이 사용하다가 DDR5부터 HfO2로 전환하기 시작했다.

High-k가 마냥 좋은 것은 아니다. 그 이유는 기존의 산화막/질화막을 증착하던 증착기로는 증착이 어렵고, ALD로을 공정을 진행해야하기 때문이다. 이에 대해 다음 항목으로 넘어가보자.

3) ALD

ALD는 앞서 전술했듯이 원자층 증착 방법으로 현재의 증착기술 중 최선단에 속한다. ALD는 큰 범주로 화학적 증착으로 CVD에 속하며, 에너지원이 열(ALD)이냐 플라즈마(PEALD)냐에 따라 나뉜다. PEALD는 공정시간이 긴 기존 ALD의 단점을 보완하며 high-k 물질 증착에 더 유리하다.

ALD는 EUV가 주도하는 반도체 미세화 트렌드와 함께하는 중요한 기술이다. EUV로 선폭이 미세화되고 여러가지 문제들이 일어나면서 소재 변화가 빠르게 변하고 있는데, 그러한 소재들을 다루기에 용이한 기술이기 때문이다. 앞서 보았던 HKMG와 D램 캐피시터 CAP이 그러하다.

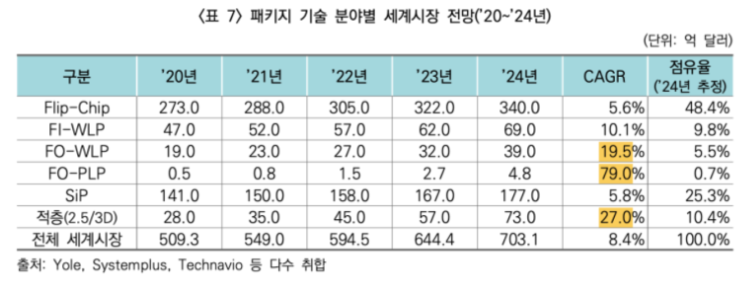

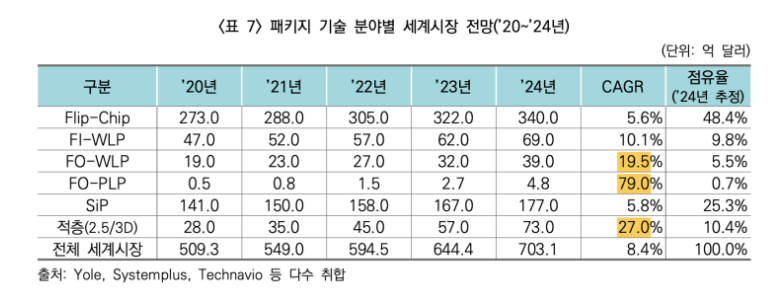

5.3 첨단(어드밴스드) 패키징

올해 반도체 세미나에서 어드밴스드 패키징을 정말 많이 다룰정도로 어드밴스드 패키징이 급속도로 성장하고 있다. 반도체 시장의 90%물량이 레거시공정으로 만들어지는 저부가가치 칩들이라는 것을 생각하면, 어드밴스드 패키징이 얼마나 적용되겠냐 싶겠지만, 이 10%도 안되는 물량이 매출액면으로 봤을때 40%이상을 차지한다고 한다.

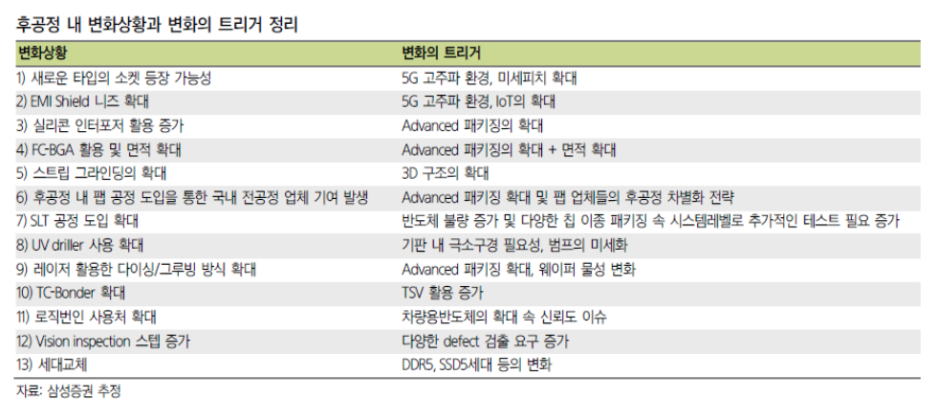

그렇다면 갑자기 왜 이렇게 후공정 시장이 주목받게 되었을까?

기존에는 반도체 제조에서 전공정을 위주로 기술발전이 크게 일어났는데, 싱글나노로 들어가고 그 발전속도가 느려지고 비용이 기하급수적으로 상승하면서 비용 대비 효율을 찾다가 후공정으로 뛰어든 것이다. 그렇게 저부가가치 사업으로 취급받던 후공정(노동집약적)에도 전공정에서 쓰이는 여러가지 고난이도 기술들을 도입하고, 전공정 기업들의 범위가 넓어지거나 반도체 팹 업체와 OSAT/기판 업체의 협업이 강화되고 있다. 후공정의 대표적인 변화들은 다음과 같다.

전술했다시피, 어드밴스드 패키징의 대부분이 후공정에 전공정 기술을 도입하는 것이라서 기술집약도가 매우 높다. OSAT업체 및 기판 업체에서만 단독적으로 진행할 수는 없고, 파운드리 기업 및 IDM 주도하에 이뤄지고 있다. 그렇기에 고부가가치 제품인 HPC향 칩 위주로 이뤄지고 있다.

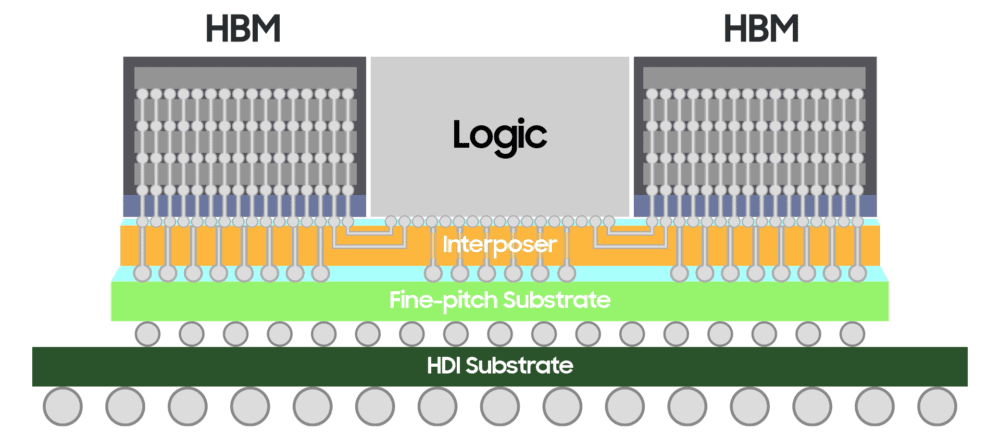

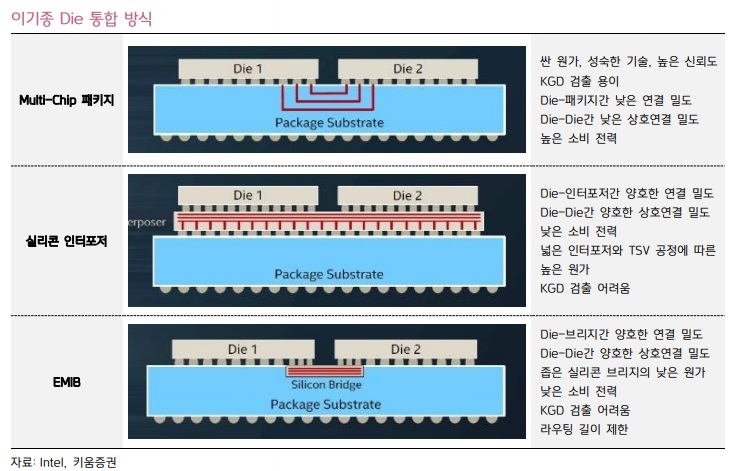

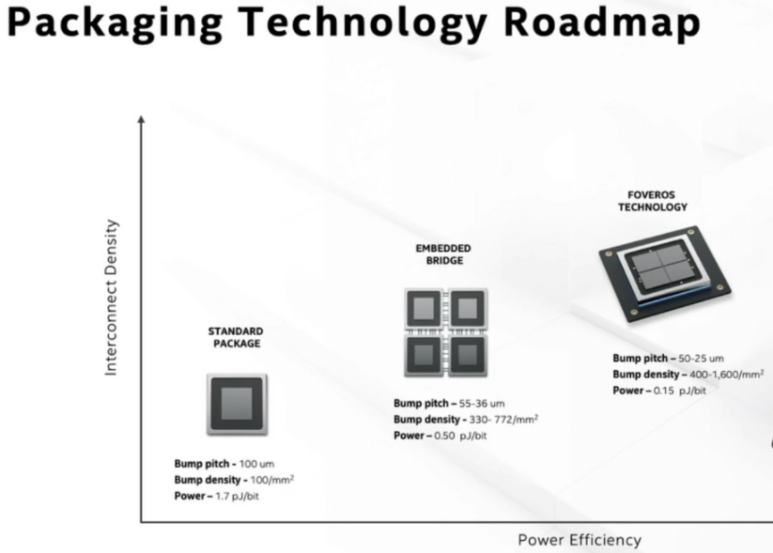

1) 이종접합 패키징(Heterogeneous Integration)

이종접합 패키징은 종류가 다른 칩을 한번에 패키징하는 것이다. 이종접합 패키징은 현재 2.5D/3D/칩렛구조로 기술이 개발중이다. 2.5D 패키지는 수평적으로 칩을 배열하고, 서로간의 원활한 배선을 위해 인터포져라는 기판을 하나 더 추가한다. 3D 패키지는 서로 다른 칩을 수직적으로 쌓아올리는 방식이다. 칩렛구조는 로직반도체 같이 여러 기능의 반도체(S램, GDDR 등등)가 모여있는 단일 칩을 기능적으로 나눠서 전공정을 진행하여 패키징하는 구조이다. 칩렛구조는 이종접합 패키징을 위해 필요한 전공정 설계기술이라고 보면 된다.

이종접합 패키징은 아직까지 하이엔드 기술이며 비용이 비싸기 떄문에 서버향이 압도적으로 많다.

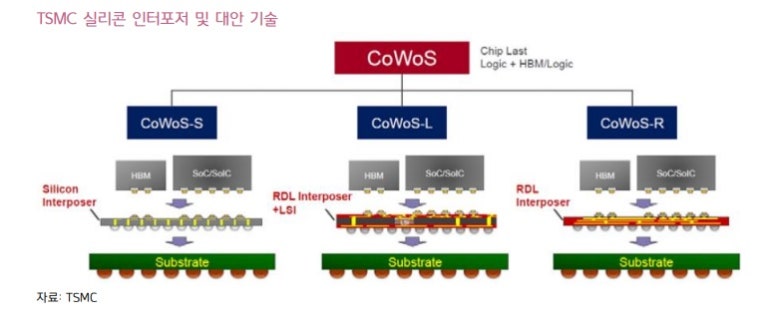

※인터포저: 이종 칩간의 연결을 위해 쓰이는 중간매개체들을 인터포저라고 한다. 어드밴스드 패키징에 쓰이는 인터포저는 미리 인터포저 안에 TSV를 형성해놓고 칩들과 RDL(재배선층)로 연결되는 방식이다. 인터포저의 선폭은 보통 5㎛이하이며, 실리콘 인터포저는 1㎛이하, EMIB는 2~3㎛이다. 하지만 실리콘 인터포저는 가격이 비싸기 때문에, 부분적으로 유기물 인터포저를 채용한다. 다음은 TSMC의 이종접합 패키징 기술로, 인터포저의 형태에 따라 기술명이 구분됨을 볼 수 있다.

TSMC 이종접합 패키징 플랫폼별 인터포저

다음은 각 기업들의 주요 이종 패키징 기술들을 정리한 것이다.

<2.5D 패키지>: 반도체 다이를 수평으로 접합한 패키징 기술이다. I/O밀도 차이가 있어 대부분 인터포저 채용이 불가피하다.

인텔

실리콘 인터포저

EMIB: 다이와 다이를 실리콘 인터포저로 연결하는데, 실리콘 인터포저를 FCBGA 기판에 내장한다. 이것을 실리콘 브리지라고 한다. 내장되어 있어 TSV공정이 덜 필요하다. 범프 피치는 36~55㎛이다.

TSMC

InFO: 인터포저 없이 FOWLP에 RDL로 로직과 메모리반도체를 수직적층한 구조. 사실상 POP다.

InFO_LSI: 인텔의 EMIB와 비슷한, 부분 실리콘 인터포저 기술.

CoWoS: FCBGA에 인터포저를 FC본딩하고 위에 칩을 FC본딩하는 방식이다. 인터포저의 형태에 따라 시리즈가 나눠진다.

FOMCM: FOWLP 기술을 사용하여 이종접합 패키징을 하는것이다.

삼전

H-CUBE: HDI 위에, 중간패키지기판 위에, 인터포저 위에 ,HBM+로직을 배치하는 기술이다. I-CUBE와 다른 점은, I-CUBE는 HBM을 4개/ H-CUBE는 6개 이상 탑재할 수 있다는 점이다.

I-CUBE: 실리콘 인터포저 위에, 로직반도체+HBM을 하나의 패키지 위에 배치하는 기술이다.

<3D 패키지>: 반도체 다이의 종류 상관없이 수직 적층을 하는 패키징 기술이다. 수직으로 배열할 경우 전자의 이동거리가 매우 짧아져 속도가 빨라진다. 현재 메모리와 로직 적층은 가능하지만, 로직간의 적층은 어렵다고 한다.

인텔

Foveros: 하이브리드본딩으로 다이끼리 연결하다, 하단 다이 자체가 인터포저 역할을 하는 것이다. 범프피치는 50~25㎛이다. TSMC의 SolC와 비슷하다.

Co-EMIB: Foveros와 EMIB기술을 합친 것으로, EMIB를 여러개 만들어 서로 연결하는 것이다.

ODI: Foveros의 상위 버전으로, TSV를 기존보다 더 크게 형성한다.

인텔 어드밴스드 패키징 로드맵

TSMC

SolC: 하이브리드 본딩을 적용하여 2.5D보다 접합부 밀도가 10배 높다.

삼전

X-CUBE: 마이크로범프 없이 로직반도체와 SRAM을 적층하는 방식.

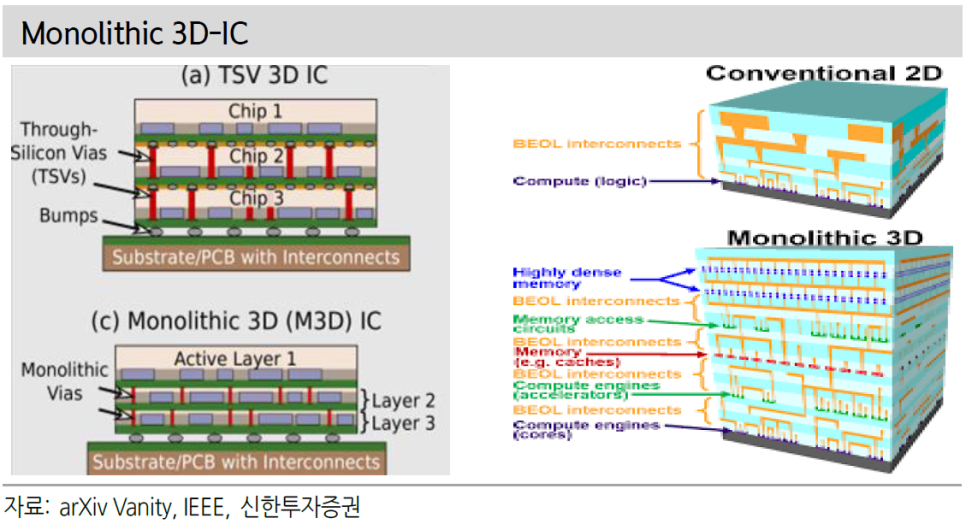

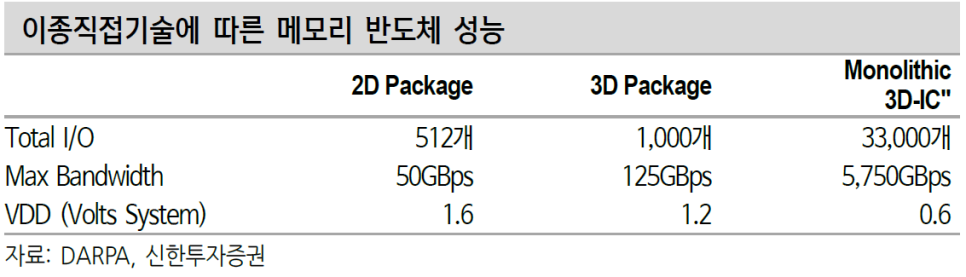

<Monolithic 3D-IC>: 후공정단에서 칩들을 배열하는 것이 아니라, 반도체 다이가 패키징 되기 전에 수직 적층하는 구조이다. 3D NAND 구조에서 서로 다른 종류의 다이들이 쌓인다고 보면 되고 후공정 기술들을 전공정에 도입하는 느낌이다. 그렇기 때문에 사실 패키징 기술은 아니지만, 이 기술이 실현되면 이종접합 패키징 시장이 다시 한번 뒤집힐 것으로 전망된다

(정인성 작가님의 이종접합 패키징 이야기)

2) 본딩의 발전

반도체 칩을 기판에 연결하는 공정을 본딩이라고 한다. 앞서 2. 후공정 항목 및 3.기판 항목에서 다뤘지만, 여기서는 칩들의 수직 적층에 초점을 둔 본딩 방식을 다룰 것이다. 적층 본딩 방식은 다음과 같이 발전해왔고, 앞서 다루지 않은 기술만 알아보자.

와이어본딩 > 플립칩 본딩 > TSV > 하이브리드 본딩

TSV: 반도체 칩에 구멍(Via)을 뚫고 금속으로 내부를 채워 위아래 연결하는 기술이다. 구멍을 Micro Bump로 채워서 다단적층을 하게 되고, 빠른 전기적 인출이 가능하도록 한다. 이때 필요한 것들이 다음과 같다.

Micro Bump

CMP: 2.1 전공정 참조.

Deep에칭: DRIE라고 부르며, 종횡비가 큰 구조를 식각할때 쓰는 기술이다.

TC본딩: TSV에 적용되는 본딩 방식 중 하나로 열압착을 이용하는 방식이다. 칩 사이에 NCF라는 절연필름을 덧대고 열을 가해서 범프 간 연결을 유도하는 방식인 TCNCP가 주류가 되고 있으며, HBM에 많이 쓰인다.

MR-MUF: TC본딩의 불균일 압력 문제를 해결하고자 도입한 TSV 기술이다. 열이나 레이저를 가해 칩 전체를 데우고, EMC로 칩 사이를 채우는 동시에 몰딩을 한다. 앞서 본 MASS REFLOW의 진화 버전으로, 오븐 대신 LAB(레이저 어시스트 본딩)를 주로 쓴다.

하이브리드본딩: 범프의 미세화에 한계가 생겨, 범프 없이 칩을 포개어버리는 방식이다. 다마신 공정을 이용해서 칩에 구리패드를 형성하고 구리 패드끼리 연결하는 방식이다.

※언더필: 칩 사이 공간을 메우는 것. TC본딩에서 언더필 공정은 캐필러리로 진행되고, MR-MUF에서는 EMC로 진행된다.

※마이크로범프: 통상 100㎛이하의 솔더 범프를 마이크로 범프라고 정의한다.

3) HBM

HBM은 D램을 적층하여 만든 새로운 고대역폭 D램이다. 처음부터 GDDR의 자리를 타겟하여 개발되었기 때문에 따로 모듈 형태로 나오지 않고, 로직반도체와 같이 패키징되어 출시되고 있다. HBM도 차세대 패키징을 이용하여 만든 제품으로 TSV기술과 인터포저가 핵심이다.

GDDR과 HBM. 핀수 자체가 넘사벽이다 > 병목현상 해결

HBM과 3D DRAM을 헷갈리기가 쉬운데, 3D DRAM은 칩 형성 과정에서 셀들을 적층하는 것이고 HBM은 만들어진 D램 다이를 적층하여 패키징하는 것이다. 즉, 전공정과 후공정의 차이라고 볼 수 있겠다.

그렇다면 왜 갑자기 HBM이 주목받게 되었을까? 아마 생성형 AI모델로 인해 AI시장이 개화되고, GPU의 시대가 도래했기 때문이 아닐까 싶다. 마침 후공정 기술이 발전하여 HBM이 GDDR의 스펙을 뛰어넘었고, '하이엔드 GPU의 증가=HBM의 증가' 가 되어버렸다. 아직까지 비용 문제로 소비자향 진입은 쉽지 않겠지만, 이미 서버향 FPGA/ASIC/CPU에 진입하였으며 점차 확대될 것으로 전망된다.

HBM은 2013년부터 개발되어 표준화를 시키고 다음과 같이 세대별로 구분된다.

HBM: 1세대. 스택당 4GB.

HBM: 2세대. 스택당 8GB.

HBM2E: 3세대. 8단. 스택당 24GB.

HBM3: 4세대. 12단. 스택당 64GB. MR-MUF공정 도입. TC본딩 대신 MASS REFLOW.

선두업체 M/S: SKH 50%, 삼전 40%, 마이크론 10%

삼전: 현재 주력제품은 HBM2(플래시볼트)와 HBM3(아이스볼트)이다. 2H23에 HB3P(스노우볼트)를 출시할 예정이다. HBM-PIM을 개발해 AMD의 'MI-100'에 탑재하였다.

SKH: 선두주자로 GPU강자 엔비디아 H100칩에 독접 공급중이다. HBM3를 제일 먼저 개발했고 올해 안에 양산 계획이라고 한다.

마이크론: GDDR에 치중하다가 타이밍을 놓쳤다.

4) FOWLP/PLP

FOWLP와 FOPLP도 성장력이 뛰어난 차세대 패키징이다. 전술했다시피 이 2개는 패키지섭스트레이트라는 개념이 아니라, RDL을 형성한 웨이퍼로 패키징하는 것이다. 아직까지 TSMC를 위주로 시장이 돌아가고 있지만, 삼전의 FOPLP가 진척되면 여러 제품군에 적용될 가능성이 높다. 또한 2.5D 및 3D 패키징과 가격 경쟁을 하며 서로의 영역을 침범할 것으로 전망된다.

5.4 화합물 반도체

화합물 반도체는 2가지 이상의 원소로 만드는 반도체다. GaN(질화갈륨)과 SiC(실리콘카바이드)가 대표적이다. 기존의 Si 반도체 대비 우수한 성능들을 가지고 있지만, 제작과정도 비교적 까다롭고 아직까지 밸류체인이 미흡하여 공급이 부족하다. 그래서 가격이 비싸고, 한정된 용도로만 쓰이고 있다.

화합물반도체는 웨이퍼 공정부터 시작하여 적용될 어플리케이션이 아직까지 불확실하다는 점에서, 화합물 반도체는 디테일보다 시장리딩을 하는 업체들의 행보가 중요하다.

화합물 반도체의 현재 주요 포인트는 다음과 같다.

6인치웨이퍼 > 8인치 웨이퍼로 업그레이드

웨이퍼의 Epitaxy성장(증착) 공정

멀티레이얼 화합물 기판: SiC on Si, Gan on SiC

AMAT의 장비 시장 독점(CMP, 증착, 이온주입 )

1) SiC 반도체

고압, 고열에도 잘 작동하고 전력 손실이 낮다. GaN보다 가격이 높다고 한다. 현재 6인치가 메인이고 8인치는 24년에 양산 시작이 될 것으로 보인다. ESS, 전기차 전력모듈, 인버터에 적용되어 전기차 시장과 함께 성장할 것으로 보인다.

SiC시장을 리딩하는 업체들은 다음과 같다.

울프스피드(웨이퍼)-STM(IDM)-테슬라(사용처)

리조넥(웨이퍼)-인피니온(IDM)-현대차(사용처)

현대오트론(IDM)-현대차(사용처)

온세미(웨이퍼~IDM)-글로벌전기차업체(사용처)

울프스피드(웨이퍼)-RFHIC(팹리스)-울프스피드(파운드리)

울프스피드(웨이퍼)-울프스피드(IDM)-GM(사용처)

울프스피드(웨이퍼)-인피니온(IDM)-폭스바겐(사용처)

코히런트(웨이퍼~IDM)-글로벌전기차업체(사용처)

덴소(IDM) - 도요타(사용처)

SiCrystal(웨이퍼)-ROHM(설계)

STM(IDM)-글로벌전기차업체(사용처)

SK실트론(웨이퍼)-예스파워테크닉스(설계)-패키징(RF머티리얼즈)-SK그룹(사용처)

DB하이텍(웨이퍼)-LX세미콘(설계)

LX세미콘(웨이퍼)-LX세모키노(설계)

KEC(IDM)-가전향 전력반도체(사용처)

(아직까지 웨이퍼에서 의미있는 숫자를 보여주는 기업은 3곳 밖에 없다. 울프스피드/투식스/SiCrystal)

근데 몇일 전 전기차 리딩업체인 테슬라가 SiC반도체 시장에 위협적인 발언을 했다. 공급이 너무 부족하여 단가가 높기 때문에 아무래도 전기차 업체 입장에선 대책을 찾을 것 같다.

2) GaN 반도체

스위칭속도가 빠르고 밴드갶이 높아서 고주파 분야에 쓰인다. 주로 라이다센서, RF, 무선충전기 등에 쓰일 것으로 보이며, BLUE LED과 같은 광소자 시장에도 침투 중이다.

GaN은 SiC대비 시장의 관심어 덜하며 아직까지 로드맵이 뚜렷한 기업이 없다. GaN을 리딩하는 업체들은 다음과 같다.

SK실트론(웨이퍼)-RFHIC+예스파워테크닉스(설계)-RF머티리얼즈(OSAT)-SK그룹(사용처)

DB하이텍+에이프로=(웨이퍼~IDM)

아모센스(IDM)

5.5 3D DRAM

3D D램은 D램을 낸드처럼 수직 적층 하는 구조이다. 그렇게 되면 미세화에 집중할 필요 없이 용량을 늘릴 수 있으므로, EUV공정 없이 높은 스펙의 D램을 제조할 수 있다. 아직까지 연구개발 중이며 업계에서는 2030년이 되어서야 상용화가 된다고 하지만, 현재 3D D램의 특허를 최다 보유한 기업이 마이크론이라는 점에서 게임체인저가 될 수 있다는 이야기가 많다.

3D D램이 상용화되면 EUV가 당장 필요하지 않으므로 고가의 EUV노광기를 이미 사들인 D램 기업들은 엄청난 손해를 보는 것이다 (삼전은 파운드리로 전환하면 되지만 SKH는 어떻게?). 마이크론이 EUV노광기 도입을 미루는 것에는 이러한 이유도 포함된다고 볼 수 있다.

5.6 AI(인공지능)

AI는 올해 초 전세계를 달궜던 핫한 키워드였다. 인공지능은 예전부터 꾸준히 연구되어 오다가, 이번 '생성형 AI모델(GPT)'의 등장으로 AI시장이 개화되었다. AI는 인간의 정보처리 능력을 모방하여 데이터를 제어하는 기술로, 핵심 하드웨어 수단이 반도체다. 폰노이만 구조로 이뤄진 컴퓨팅 시스템과 인간의 뇌는 다르지만, 신경 하나하나가 인간의 뇌를 구성하듯 반도체 하나하나가 AI 시스템을 만든다고 이해하면 된다.

AI가 반도체 산업에 끼친 영역은 크게 2가지로 불 수 있는데, 첫째는 머신러닝에 적합한 병렬 연산 반도체 시장이고, 두번째는 늘어나는 데이터 처리량에 필요한 서버향 반도체 시장이다.

AI의 머신러닝은 수 많은 데이터를 빠르게 계산하는데 초점이 맞춰져 있다. 그래서 고도의 연산보다 병렬 연산이 중요하여 GPU가 채택된 것이다. 현재 엔비디아의 주가가 그것을 보여주고 있으며, 엔비디아의 A100과 H100은 공급 부족이 일어나고 있다. 이 GPU에 HBM이 탑재된다는 것 또한 반도체 시장에 큰 영향을 끼치고 있다.

두번째로 끼친 영향은 데이터 처리량으로 인한 서버향 반도체라고 했는데, 이 AI는 우리 인간이 만들어낸 데이터들을 기반으로 학습을 하는 존재다. 즉, 데이터가 무수히 많은 서버에서 정보를 구해 공부를 하고, 그로부터 생산한 데이터들을 다시 서버에 가져다 놓기도 한다. 빅테크 기업들의 각 AI모델들이 쉬지 않고 데이터를 처리하고 있으니 그 양은 기하급수적으로 늘고 있다. 모바일 및 PC시장이 정체되고 서버향 마저 그 성장세가 가라앉고 있던 최근, 이러한 영향은 결코 무시할 수 없다.

기업까지 다 다루려고 했는데 분량 조절도 실패하고 예상보다 발행일도 미뤄졌습니다 ㅠㅠ 반붐온이 오기 전에 포스팅하고 싶었는데 진짜 간발의차...(근데 반붐온 맞겠쥬?) 부족한 부분을 다듬어 [2편.기업편]으로 다시 찾아뵙겠습니다.

반도체 가즈아~~~~~~~~

* 본 포스팅은 비전문가의 지식으로 틀린 부분이 있을 수 있습니다. 내용 관련하여 부족한 부분뿐만 아니라 가독성 관련하여 부족한 부분도 지적해주시면 대단히 감사합니다!

<참고자료>

댓글 0

첫번째 댓글을 남겨주세요